- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4274 > XA3S500E-4FTG256Q (Xilinx Inc)IC FPGA SPARTAN-3E 500K 256FTBGA PDF資料下載

參數(shù)資料

| 型號: | XA3S500E-4FTG256Q |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 23/37頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3E XA |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 190 |

| 門數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 125°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

DS635 (v2.0) September 9, 2009

Product Specification

3

R

Configuration

XA Spartan-3E FPGAs are programmed by loading config-

uration data into robust, reprogrammable, static CMOS con-

figuration latches (CCLs) that collectively control all

functional elements and routing resources. The FPGA’s

configuration data is stored externally in a PROM or some

other non-volatile medium, either on or off the board. After

applying power, the configuration data is written to the

FPGA using any of five different modes:

Serial Peripheral Interface (SPI) from an

industry-standard SPI serial Flash

Byte Peripheral Interface (BPI) Up or Down from an

industry-standard x8 or x8/x16 parallel NOR Flash

Slave Serial, typically downloaded from a processor

Slave Parallel, typically downloaded from a processor

Boundary Scan (JTAG), typically downloaded from a

processor or system tester.

I/O Capabilities

The XA Spartan-3E FPGA SelectIO interface supports

many popular single-ended and differential standards.

Table 2 shows the number of user I/Os as well as the num-

ber of differential I/O pairs available for each device/pack-

age combination.

XA Spartan-3E FPGAs support the following single-ended

standards:

3.3V low-voltage TTL (LVTTL)

Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V,

1.5V, or 1.2V

3V PCI at 33 MHz

HSTL I and III at 1.8V, commonly used in memory

applications

SSTL I at 1.8V and 2.5V, commonly used for memory

applications

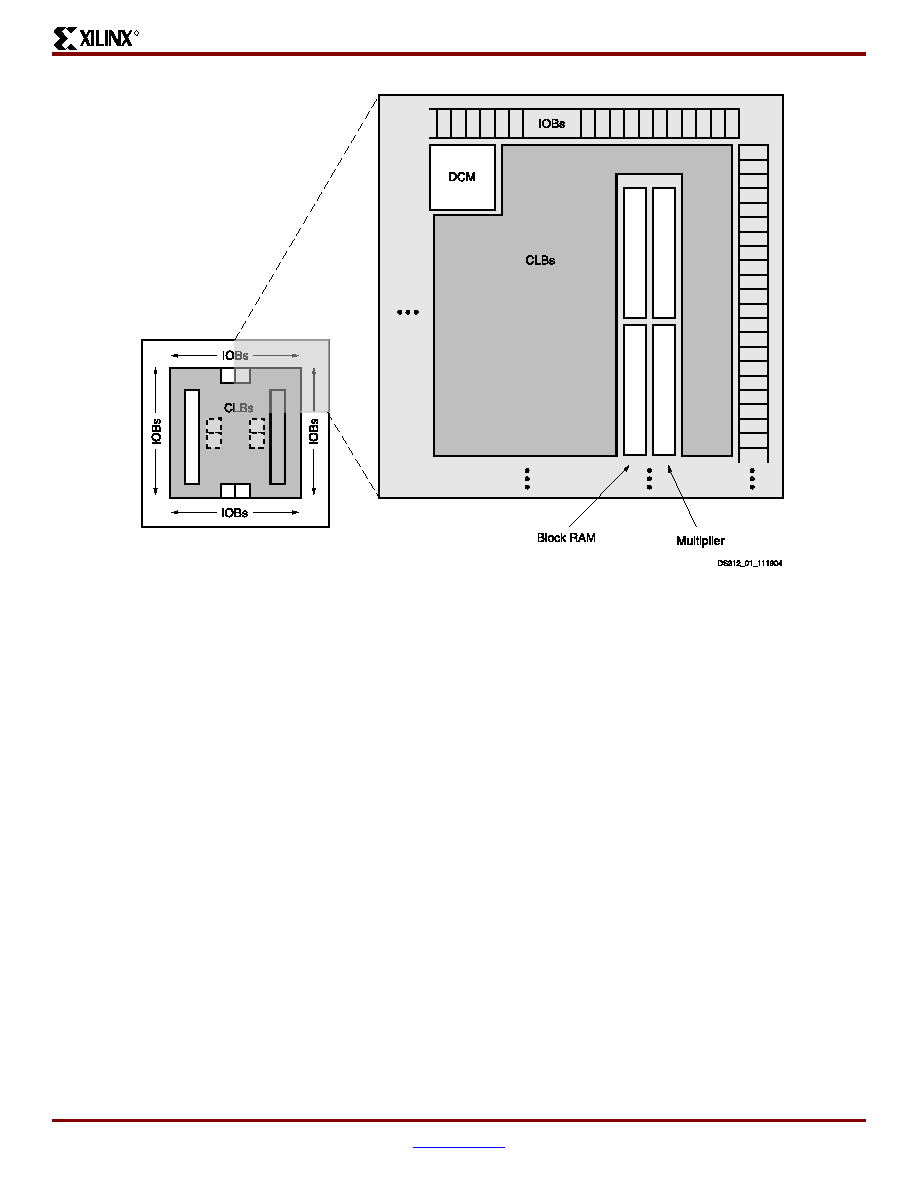

Figure 1: XA Spartan-3E Family Architecture

Notes:

1.

The XA3S1200E and XA3S1600E have two additional DCMs on both the left and right sides as

indicated by the dashed lines. The XA3S100E has only one DCM at the top and one at the bottom.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 93AA86AT-I/ST | IC EEPROM 16KBIT 2048X8 8-TSSOP |

| XA2S200E-6FT256Q | IC FPGA SPARTAN-IIE 256FPBGA |

| 93AA86AT-I/MS | IC EEPROM 16KBIT 2048X8 8-MSOP |

| XC3S700A-5FG400C | IC SPARTAN-3A FPGA 700K 400FBGA |

| XC2S200-5FG456C | IC FPGA 2.5V 1176 CLB'S 456-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA3S500E-4PQG208I | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4PQG208Q | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S50-4PQG208I | 功能描述:IC FPGA SPARTAN-3 50K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S50-4PQG208Q | 功能描述:IC FPGA SPARTAN-3 50K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S50-4VQG100I | 功能描述:IC FPGA SPARTAN-3 50K 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。