- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4274 > XA3S500E-4FTG256Q (Xilinx Inc)IC FPGA SPARTAN-3E 500K 256FTBGA PDF資料下載

參數(shù)資料

| 型號: | XA3S500E-4FTG256Q |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 26/37頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3E XA |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計: | 368640 |

| 輸入/輸出數(shù): | 190 |

| 門數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 125°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

DS635 (v2.0) September 9, 2009

Product Specification

32

R

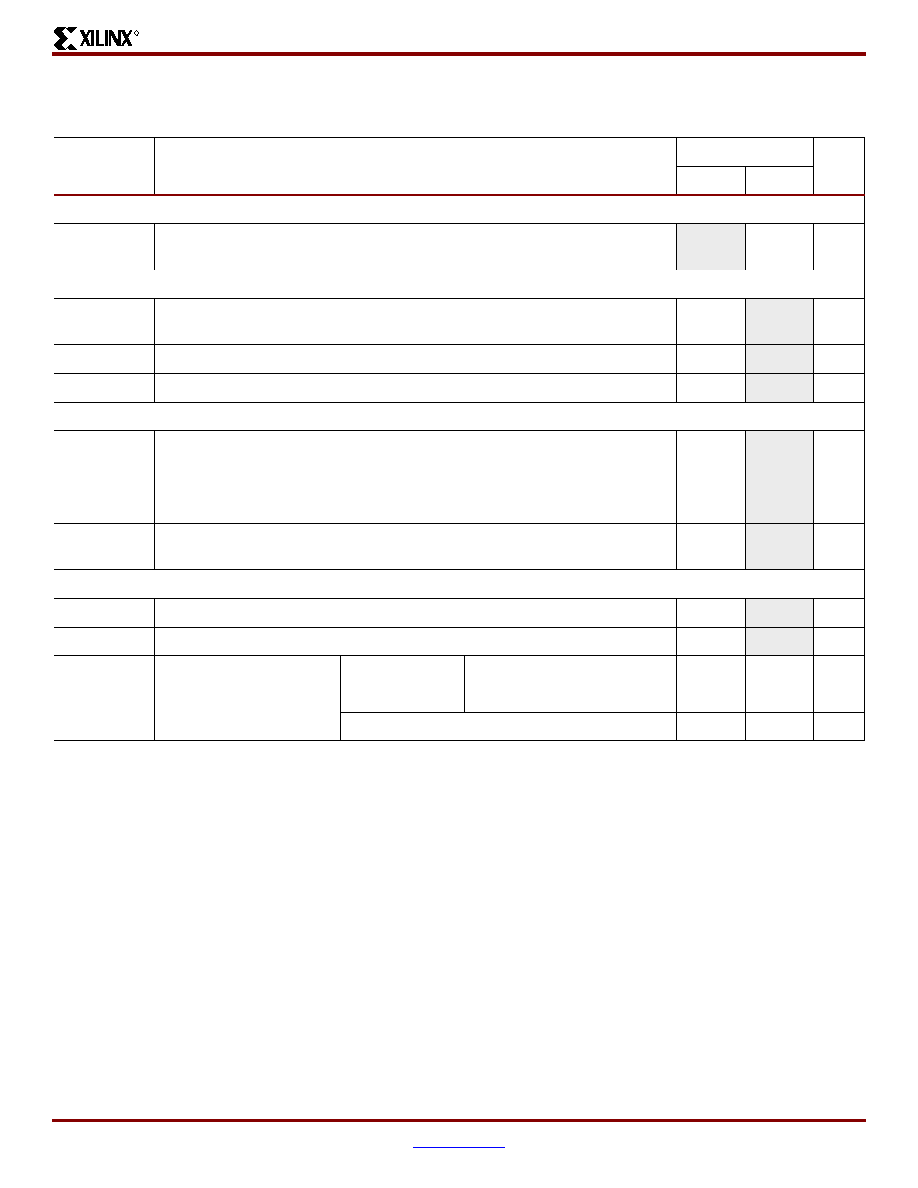

Slave Parallel Mode Timing

Table 39: Timing for the Slave Parallel Configuration Mode

Symbol

Description

-4 Speed Grade

Units

Min

Max

Clock-to-Output Times

TSMCKBY

The time from the rising transition on the CCLK pin to a signal transition at the

BUSY pin

-12.0

ns

Setup Times

TSMDCC

The time from the setup of data at the D0-D7 pins to the active edge the CCLK

pin

11.0

-ns

TSMCSCC

Setup time on the CSI_B pin before the active edge of the CCLK pin

10.0

-ns

TSMCCW(2)

Setup time on the RDWR_B pin before active edge of the CCLK pin

23.0

-ns

Hold Times

TSMCCD

The time from the active edge of the CCLK pin to the point when data is last

held at the D0-D7 pins

1.0

-ns

TSMCCCS

The time from the active edge of the CCLK pin to the point when a logic level

is last held at the CSO_B pin

0

-ns

TSMWCC

The time from the active edge of the CCLK pin to the point when a logic level

is last held at the RDWR_B pin

0

-ns

Clock Timing

TCCH

The High pulse width at the CCLK input pin

5

-ns

TCCL

The Low pulse width at the CCLK input pin

5

-ns

FCCPAR

Frequency of the clock

signal at the CCLK input

pin

No bitstream

compression

Not using the BUSY pin(2)

050

MHz

Using the BUSY pin

0

66

MHz

With bitstream compression

0

20

MHz

Notes:

1.

The numbers in this table are based on the operating conditions set forth in Table 6.

2.

In the Slave Parallel mode, it is necessary to use the BUSY pin when the CCLK frequency exceeds this maximum specification.

3.

Some Xilinx documents refer to Parallel modes as “SelectMAP” modes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 93AA86AT-I/ST | IC EEPROM 16KBIT 2048X8 8-TSSOP |

| XA2S200E-6FT256Q | IC FPGA SPARTAN-IIE 256FPBGA |

| 93AA86AT-I/MS | IC EEPROM 16KBIT 2048X8 8-MSOP |

| XC3S700A-5FG400C | IC SPARTAN-3A FPGA 700K 400FBGA |

| XC2S200-5FG456C | IC FPGA 2.5V 1176 CLB'S 456-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA3S500E-4PQG208I | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4PQG208Q | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S50-4PQG208I | 功能描述:IC FPGA SPARTAN-3 50K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S50-4PQG208Q | 功能描述:IC FPGA SPARTAN-3 50K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S50-4VQG100I | 功能描述:IC FPGA SPARTAN-3 50K 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。