- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19312 > XC2S15-5VQG100C (Xilinx Inc)IC SPARTAN-II FPGA 15K 100-VQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S15-5VQG100C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 48/99頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SPARTAN-II FPGA 15K 100-VQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 96 |

| 邏輯元件/單元數(shù): | 432 |

| RAM 位總計(jì): | 16384 |

| 輸入/輸出數(shù): | 60 |

| 門(mén)數(shù): | 15000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

| 產(chǎn)品目錄頁(yè)面: | 599 (CN2011-ZH PDF) |

| 其它名稱: | 122-1309 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)當(dāng)前第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)

Spartan-II FPGA Family: DC and Switching Characteristics

DS001-3 (v2.8) June 13, 2008

Module 3 of 4

Product Specification

52

R

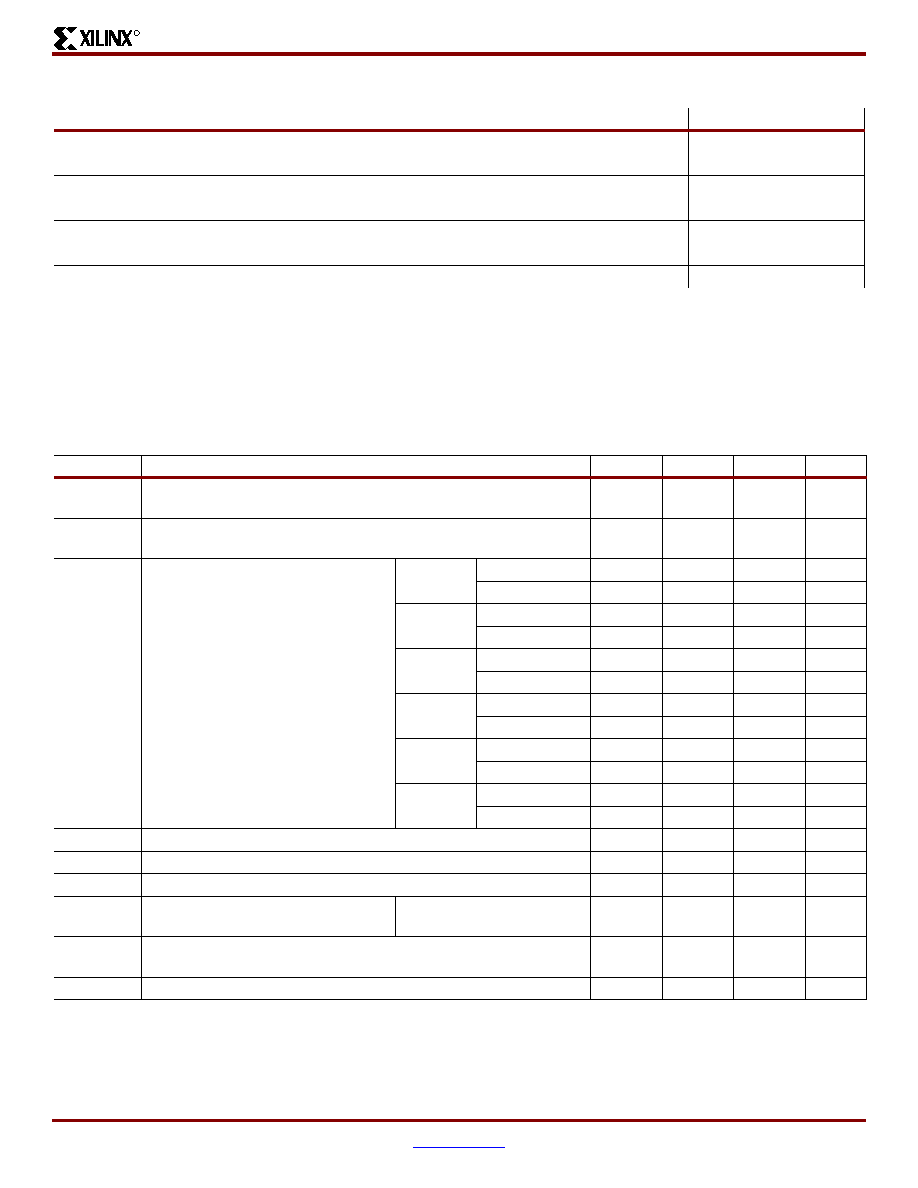

Recommended Operating Conditions

DC Characteristics Over Operating Conditions

Symbol

Description

Min

Max

Units

TJ

Junction temperature(1)

Commercial

0

85

°C

Industrial

–40

100

°C

VCCINT

Supply voltage relative to GND(2,5)

Commercial

2.5 – 5%

2.5 + 5%

V

Industrial

2.5 – 5%

2.5 + 5%

V

VCCO

Supply voltage relative to GND(3,5)

Commercial

1.4

3.6

V

Industrial

1.4

3.6

V

TIN

Input signal transition time(4)

-

250

ns

Notes:

1.

At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per

°C.

2.

Functional operation is guaranteed down to a minimum VCCINT of 2.25V (Nominal VCCINT – 10%). For every 50 mV reduction in

VCCINT below 2.375V (nominal VCCINT – 5%), all delay parameters increase by 3%.

3.

Minimum and maximum values for VCCO vary according to the I/O standard selected.

4.

Input and output measurement threshold is ~50% of VCCO. See "Delay Measurement Methodology," page 60 for specific levels.

5.

Supply voltages may be applied in any order desired.

Symbol

Description

Min

Typ

Max

Units

VDRINT

Data Retention VCCINT voltage (below which configuration data

may be lost)

2.0

-

V

VDRIO

Data Retention VCCO voltage (below which configuration data may

be lost)

1.2

-

V

ICCINTQ

Quiescent VCCINT supply current(1)

XC2S15

Commercial

-

10

30

mA

Industrial

-

10

60

mA

XC2S30

Commercial

-

10

30

mA

Industrial

-

10

60

mA

XC2S50

Commercial

-

12

50

mA

Industrial

-

12

100

mA

XC2S100

Commercial

-

12

50

mA

Industrial

-

12

100

mA

XC2S150

Commercial

-

15

50

mA

Industrial

-

15

100

mA

XC2S200

Commercial

-

15

75

mA

Industrial

-

15

150

mA

ICCOQ

Quiescent VCCO supply current(1)

--

2

mA

IREF

VREF current per VREF pin

-

20

μA

IL

Input or output leakage current(2)

–10

-

+10

μA

CIN

Input capacitance (sample tested)

VQ, CS, TQ, PQ, FG

packages

--

8

pF

IRPU

Pad pull-up (when selected) @ VIN = 0V, VCCO = 3.3V

(sample tested)(3)

--

0.25

mA

IRPD

Pad pull-down (when selected) @ VIN = 3.6V (sample tested)(3)

--

0.15

mA

Notes:

1.

With no output current loads, no active input pull-up resistors, all I/O pins 3-stated and floating.

2.

The I/O leakage current specification applies only when the VCCINT and VCCO supply voltages have reached their respective

minimum Recommended Operating Conditions.

3.

Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down resistors

do not provide valid logic levels when input pins are connected to other circuits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EEM12DSXN | CONN EDGECARD 24POS DIP .156 SLD |

| RSA43DRMH | CONN EDGECARD 86POS .125 SQ WW |

| TACL335M004H | CAP TANT 3.3UF 4V 20% 0603 |

| KA79L05AZBU | IC REG LDO -5V .1A TO-92 |

| EEM12DSXH | CONN EDGECARD 24POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S15-5VQG100I | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 15K GATES 432 CELLS 263MHZ 2.5V 100VTQFP - Trays 制造商:Xilinx 功能描述:IC SYSTEM GATE |

| XC2S15-6CS144C | 功能描述:IC FPGA 2.5V C-TEMP 144-CSBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-II 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門(mén)數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類(lèi)型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC2S15-6CS144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S15-6CSG144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S15-6CSG144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。