- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4277 > XC2S200-5FGG456C (Xilinx Inc)IC SPARTAN-II FPGA 200K 456-FBGA PDF資料下載

參數(shù)資料

| 型號: | XC2S200-5FGG456C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 22/99頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-II FPGA 200K 456-FBGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 1176 |

| 邏輯元件/單元數(shù): | 5292 |

| RAM 位總計(jì): | 57344 |

| 輸入/輸出數(shù): | 284 |

| 門數(shù): | 200000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 456-BBGA |

| 供應(yīng)商設(shè)備封裝: | 456-FBGA |

| 其它名稱: | 122-1312 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

29

R

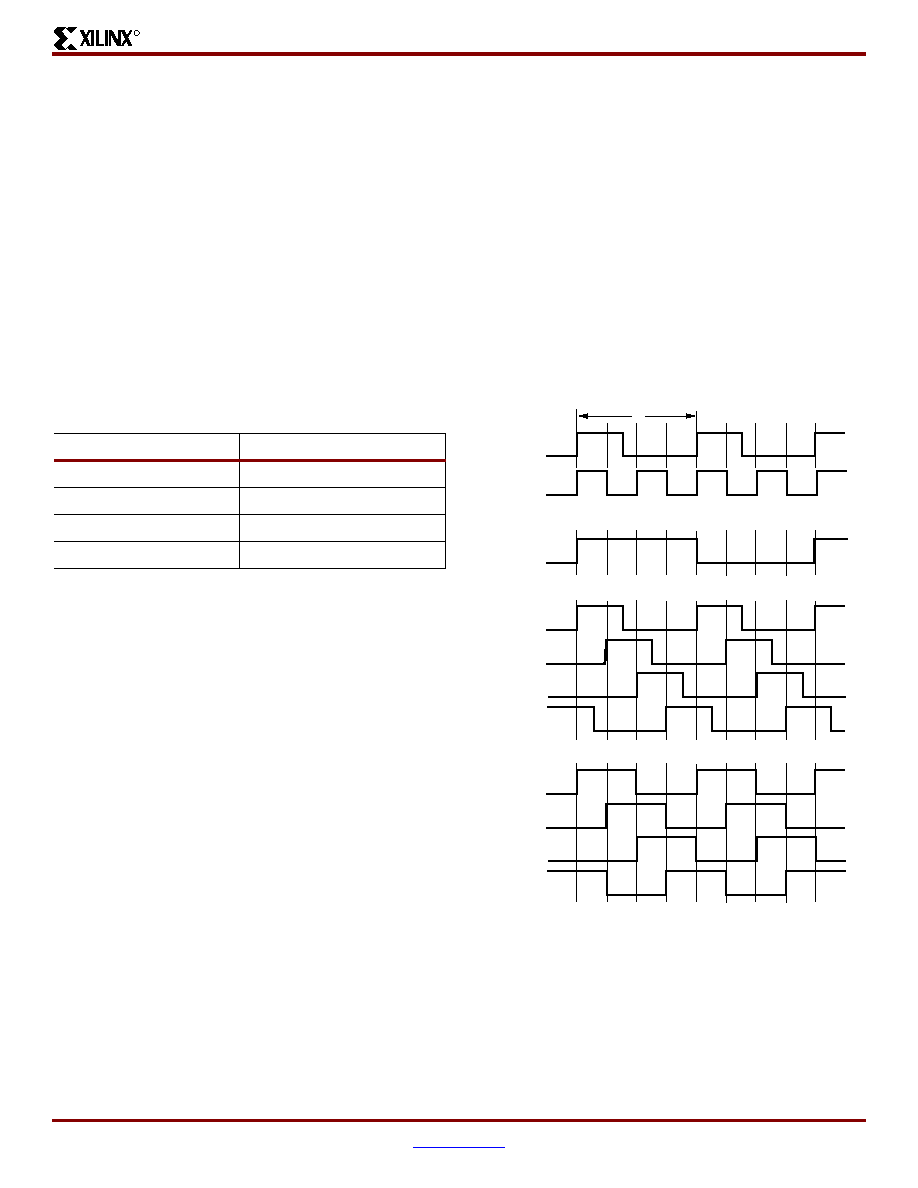

division factor N except for non-integer division in High

Frequency (HF) mode. For division factor 1.5 the duty cycle

in the HF mode is 33.3% High and 66.7% Low. For division

factor 2.5, the duty cycle in the HF mode is 40.0% High and

60.0% Low.

1x Clock Outputs — CLK[0|90|180|270]

The 1x clock output pin CLK0 represents a

delay-compensated version of the source clock (CLKIN)

signal. The CLKDLL primitive provides three phase-shifted

versions of the CLK0 signal while CLKDLLHF provides only

the 180 degree phase-shifted version. The relationship

between phase shift and the corresponding period shift

appears in Table 10.

The timing diagrams in Figure 26 illustrate the DLL clock

output characteristics.

The DLL provides duty cycle correction on all 1x clock

outputs such that all 1x clock outputs by default have a

50/50 duty cycle. The DUTY_CYCLE_CORRECTION

property (TRUE by default), controls this feature. In order to

deactivate the DLL duty cycle correction, attach the

DUTY_CYCLE_CORRECTION=FALSE property to the

DLL primitive. When duty cycle correction deactivates, the

output clock has the same duty cycle as the source clock.

The DLL clock outputs can drive an OBUF, a BUFG, or they

can route directly to destination clock pins. The DLL clock

outputs can only drive the BUFGs that reside on the same

edge (top or bottom).

Locked Output — LOCKED

In order to achieve lock, the DLL may need to sample

several thousand clock cycles. After the DLL achieves lock

the LOCKED signal activates. The "DLL Timing

Parameters" section of Module 3 provides estimates for

locking times.

In order to guarantee that the system clock is established

prior to the device "waking up," the DLL can delay the

completion of the device configuration process until after

the DLL locks. The STARTUP_WAIT property activates this

feature.

Until the LOCKED signal activates, the DLL output clocks

are not valid and can exhibit glitches, spikes, or other

spurious movement. In particular the CLK2X output will

appear as a 1x clock with a 25/75 duty cycle.

DLL Properties

Properties provide access to some of the Spartan-II family

DLL features, (for example, clock division and duty cycle

correction).

Duty Cycle Correction Property

The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270,

use the duty-cycle corrected default, such that they exhibit a

50/50 duty cycle. The DUTY_CYCLE_CORRECTION

property (by default TRUE) controls this feature. To

deactivate the DLL duty-cycle correction for the 1x clock

outputs, attach the DUTY_CYCLE_CORRECTION=FALSE

property to the DLL primitive.

Clock Divide Property

The CLKDV_DIVIDE property specifies how the signal on

the CLKDV pin is frequency divided with respect to the

CLK0 pin. The values allowed for this property are 1.5, 2,

2.5, 3, 4, 5, 8, or 16; the default value is 2.

Table 10: Relationship of Phase-Shifted Output Clock

to Period Shift

Phase (degrees)

Period Shift (percent)

00%

90

25%

180

50%

270

75%

Figure 26: DLL Output Characteristics

DS001_26_032300

CLKIN

CLK2X

CLK0

CLK90

CLK180

CLK270

CLKDV

CLKDV_DIVIDE = 2

DUTY_CYCLE_CORRECTION = FALSE

CLK0

CLK90

CLK180

CLK270

DUTY_CYCLE_CORRECTION = TRUE

T

0

90 180 270

0

90 180 270

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 745777-4 | CONN D-SUB GASKET RFI 37POS TIN |

| 24LC32AFT-E/MNY | IC SRL EEPROM 4KX8 2.5V 8-TDFN |

| XC3S700A-4FG400I | IC SPARTAN-3A FPGA 700K 400FBGA |

| 554043-2 | CONN STANDOFF M3.5 SCKT #6-32 |

| 24LC64FT-E/SN | IC SRL EEPROM 8KX8 2.5V 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S200-5FGG456C4124 | 制造商:Xilinx 功能描述: |

| XC2S200-5FGG456I | 功能描述:IC SPARTAN-II FPGA 200K 456-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S200-5PQ208C | 功能描述:IC FPGA 2.5V 1176 CLB'S 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S200-5PQ208I | 功能描述:IC FPGA 2.5V I-TEMP 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S200-5PQ208Q | 制造商:Xilinx 功能描述:XILINX XC2S200-5PQ208Q FPGA - Trays 制造商:Xilinx 功能描述:Xilinx XC2S200-5PQ208Q FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。