- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S400E-7FG676C FPGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S400E-7FG676C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁(yè)數(shù): | 16/21頁(yè) |

| 文件大?。?/td> | 183K |

| 代理商: | XC2S400E-7FG676C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

16

www.xilinx.com

1-800-255-7778

DS077-3 (v2.0) November 18, 2002

Product Specification

R

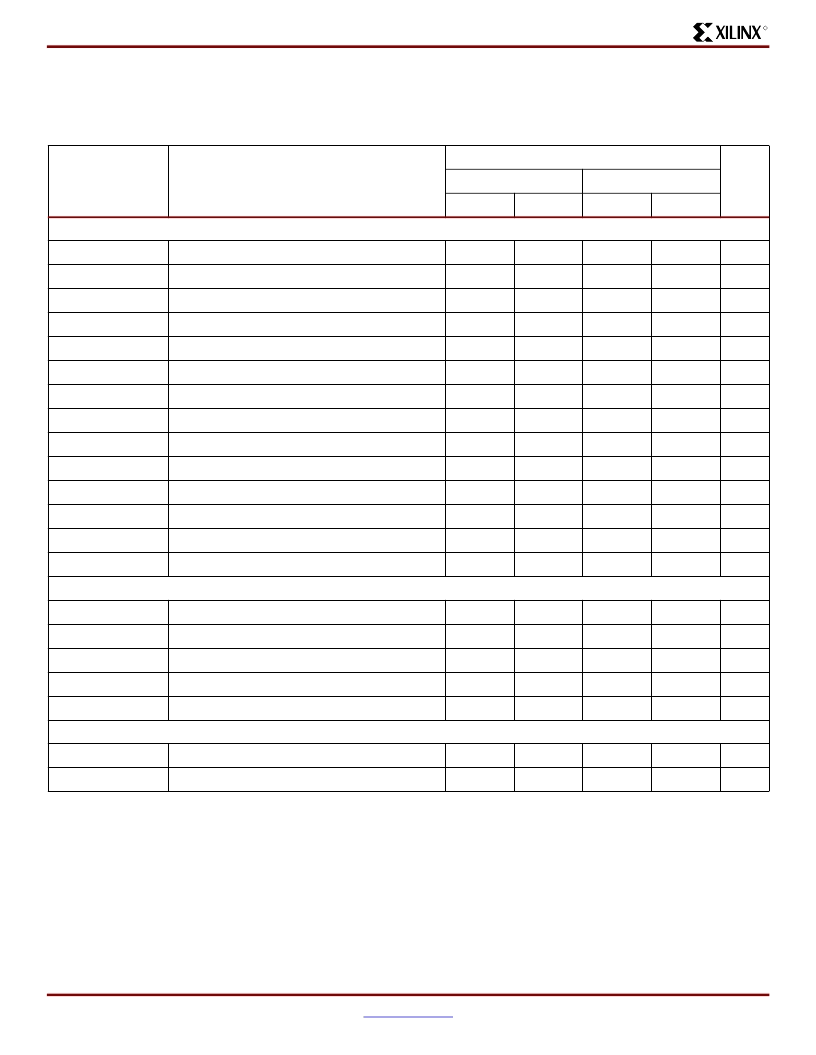

CLB Arithmetic Switching Characteristics

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment

listed. Precise values are provided by the timing analyzer.

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Combinatorial Delays

T

OPX

T

OPXB

T

OPY

T

OPYB

T

OPCYF

T

OPGY

T

OPGYB

T

OPCYG

T

BXCY

T

CINX

T

CINXB

T

CINY

T

CINYB

T

BYP

F operand inputs to X via XOR

-

0.8

-

0.8

ns

F operand input to XB output

-

0.8

-

0.9

ns

F operand input to Y via XOR

-

1.4

-

1.5

ns

F operand input to YB output

-

1.1

-

1.3

ns

F operand input to COUT output

-

0.9

-

1.0

ns

G operand inputs to Y via XOR

-

0.8

-

0.9

ns

G operand input to YB output

-

1.2

-

1.3

ns

G operand input to COUT output

-

0.9

-

1.0

ns

BX initialization input to COUT

-

0.51

-

0.6

ns

CIN input to X output via XOR

-

0.6

-

0.7

ns

CIN input to XB

-

0.07

-

0.1

ns

CIN input to Y via XOR

-

0.7

-

0.7

ns

CIN input to YB

-

0.4

-

0.5

ns

CIN input to COUT output

-

0.14

-

0.15

ns

Multiplier Operation

T

FANDXB

T

FANDYB

T

FANDCY

T

GANDYB

T

GANDCY

Setup/Hold Times with Respect to Clock CLK

F1/2 operand inputs to XB output via AND

-

0.35

-

0.4

ns

F1/2 operand inputs to YB output via AND

-

0.7

-

0.8

ns

F1/2 operand inputs to COUT output via AND

-

0.5

-

0.6

ns

G1/2 operand inputs to YB output via AND

-

0.6

-

0.7

ns

G1/2 operand inputs to COUT output via AND

-

0.3

-

0.4

ns

T

CCKX

/ T

CKCX

T

CCKY

/ T

CKCY

CIN input to FFX

1.2 / 0

-

1.3 / 0

-

ns

CIN input to FFY

1.2 / 0

-

1.3 / 0

-

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S400E-7FT256C | FPGA |

| XC2S600E-6FG456C | FPGA |

| XC2S600E-6FG456I | FPGA |

| XC2S600E-6FG676C | FPGA |

| XC2S600E-6FG676I | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S400E-7FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG456C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。