- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S400E-7FG676C FPGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S400E-7FG676C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 2/21頁 |

| 文件大?。?/td> | 183K |

| 代理商: | XC2S400E-7FG676C |

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

2

www.xilinx.com

1-800-255-7778

DS077-3 (v2.0) November 18, 2002

Product Specification

R

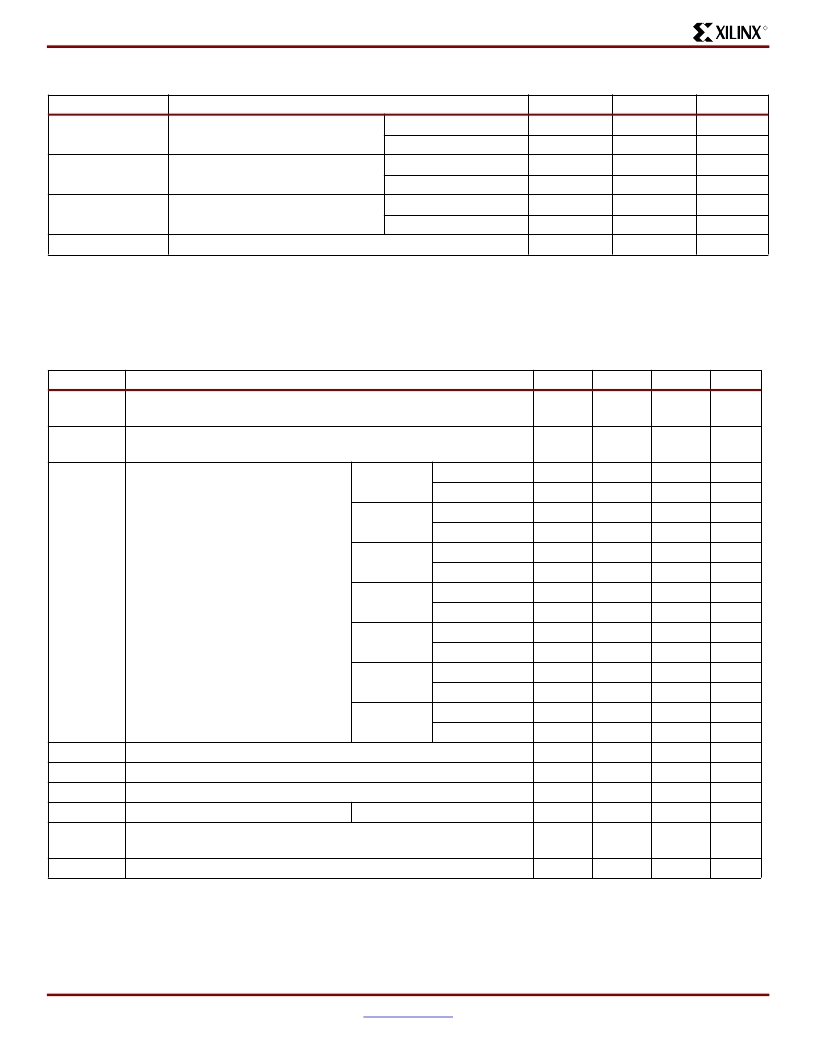

Recommended Operating Conditions

DC Characteristics Over Operating Conditions

Symbol

T

J

Description

Min

0

–

40

Max

85

100

Units

°

C

°

C

V

V

V

V

ns

Junction temperature

Commercial

Industrial

Commercial

Industrial

Commercial

Industrial

V

CCINT

Supply voltage relative to GND

(1)

1.8

–

5%

1.8

–

5%

1.2

1.2

-

1.8 + 5%

1.8 + 5%

3.6

3.6

250

V

CCO

Supply voltage relative to GND

(2)

T

IN

Input signal transition time

(3)

Notes:

1.

Functional operation is guaranteed down to a minimum V

of 1.62V (Nominal V

CCINT

–

10%). For every 50 mV reduction in

V

CCINT

below 1.71V (nominal V

CCINT

–

5%), all delay parameters increase by 3%.

Minimum and maximum values for V

CCO

vary according to the I/O standard selected.

Input and output measurement threshold is ~50% of V

CCO

.

2.

3.

Symbol

V

DRINT

Description

Min

1.5

Typ

-

Max

-

Units

V

Data retention V

CCINT

voltage (below which configuration data may

be lost)

Data retention V

CCO

voltage (below which configuration data may

be lost)

Quiescent V

CCINT

supply current

(1)

V

DRIO

1.2

-

-

V

I

CCINTQ

XC2S50E

Commercial

Industrial

Commercial

Industrial

Commercial

Industrial

Commercial

Industrial

Commercial

Industrial

Commercial

Industrial

Commercial

Industrial

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

200

200

200

200

300

300

300

300

300

300

300

300

400

400

2

20

+10

8

0.25

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

μ

A

μ

A

pF

mA

XC2S100E

XC2S150E

XC2S200E

XC2S300E

XC2S400E

XC2S600E

I

CCOQ

I

REF

I

L

C

IN

I

RPU

Quiescent V

CCO

supply current

(1)

V

REF

current per V

REF

pin

Input or output leakage current

(2)

Input capacitance (sample tested)

Pad pull-up (when selected) @ V

IN

= 0V, V

CCO

= 3.3V

(sample tested)

(3)

Pad pull-down (when selected) @ V

IN

= 3.6V (sample tested)

(3)

–

10

-

-

TQ, PQ, FG, FT packages

I

RPD

-

-

0.25

mA

Notes:

1.

2.

With no output current loads, no active input pull-up resistors, all I/O pins 3-stated and floating.

The I/O leakage current specification applies only when the V

CCINT

and V

CCO

supply voltages have reached their respective

minimum Recommended Operating Conditions.

Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down

resistors do not provide valid logic levels when input pins are connected to other circuits.

3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S400E-7FT256C | FPGA |

| XC2S600E-6FG456C | FPGA |

| XC2S600E-6FG456I | FPGA |

| XC2S600E-6FG676C | FPGA |

| XC2S600E-6FG676I | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S400E-7FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG456C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。