- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1973 > XC3S400AN-4FG400I (Xilinx Inc)IC FPGA SPARTAN 3AN 400FBGA PDF資料下載

參數(shù)資料

| 型號: | XC3S400AN-4FG400I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 29/123頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 3AN 400FBGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計: | 368640 |

| 輸入/輸出數(shù): | 311 |

| 門數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 400-BGA |

| 供應(yīng)商設(shè)備封裝: | 400-FBGA(21x21) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

Spartan-3AN FPGA Family: DC and Switching Characteristics

DS557 (v4.1) April 1, 2011

Product Specification

13

Power Supply Specifications

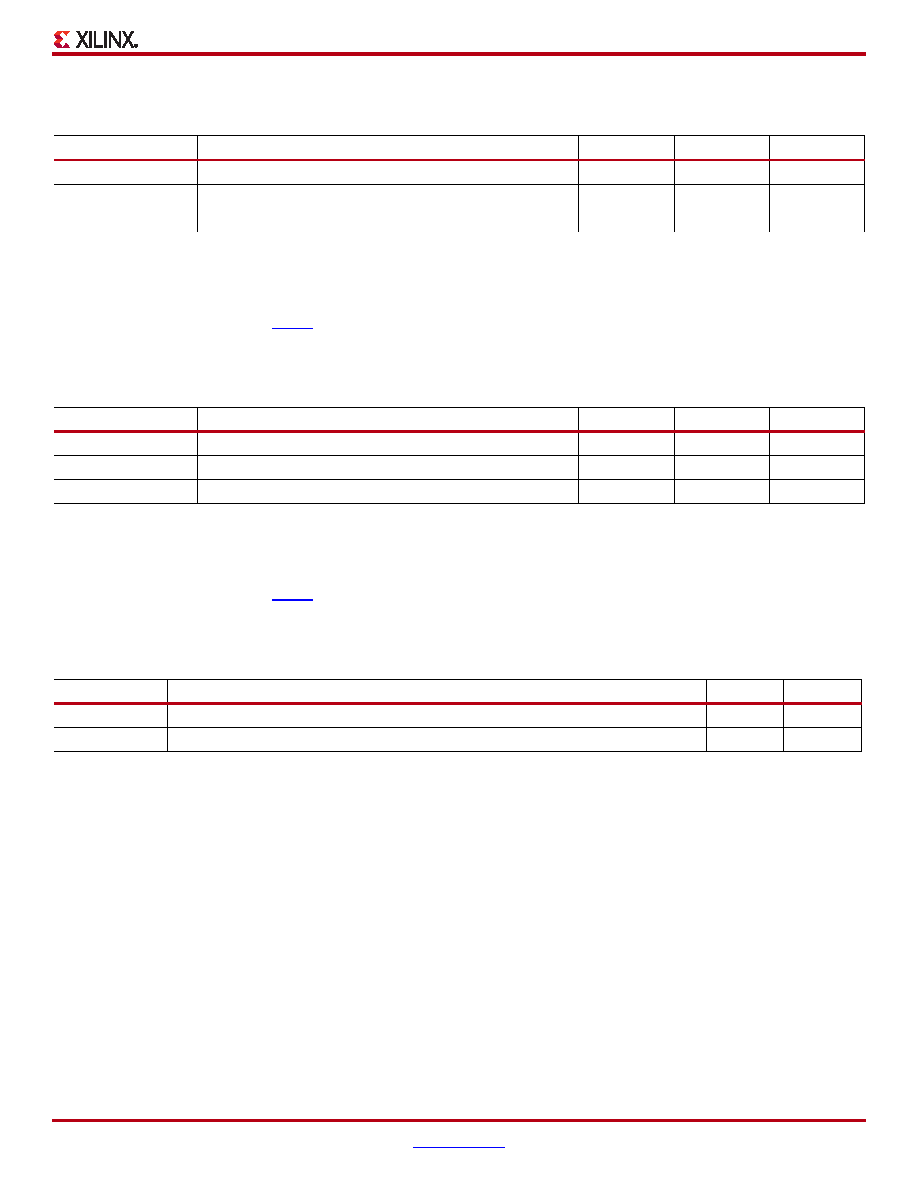

Table 7: Supply Voltage Thresholds for Power-On Reset

Symbol

Description

Min

Max

Units

VCCINTT

Threshold for the VCCINT supply

0.4

1.0

V

VCCAUXT

Threshold for the VCCAUX supply

1.0

2.0

V

VCCO2T

Threshold for the VCCO Bank 2 supply

1.0

2.0

V

Notes:

1.

When configuring from the In-System Flash, VCCAUX must be in the recommended operating range; on power-up make sure VCCAUX

reaches at least 3.0V before INIT_B goes High to indicate the start of configuration. VCCINT, VCCAUX, and VCCO supplies to the FPGA can

be applied in any order if this requirement is met. However, an external configuration source might have specific requirements. Check the

data sheet for the attached configuration source. Apply VCCINT last for lowest overall power consumption (see the chapter called “Powering

Spartan-3 Generation FPGAs” in UG331 for more information).

2.

To ensure successful power-on, VCCINT, VCCO Bank 2, and VCCAUX supplies must rise through their respective threshold-voltage ranges with

no dips at any point.

Table 8: Supply Voltage Ramp Rate

Symbol

Description

Min

Max

Units

VCCINTR

Ramp rate from GND to valid VCCINT supply level

0.2

100

ms

VCCAUXR

Ramp rate from GND to valid VCCAUX supply level

0.2

100

ms

VCCO2R

Ramp rate from GND to valid VCCO Bank 2 supply level

0.2

100

ms

Notes:

1.

When configuring from the In-System Flash, VCCAUX must be in the recommended operating range; on power-up make sure VCCAUX

reaches at least 3.0V before INIT_B goes High to indicate the start of configuration. VCCINT, VCCAUX, and VCCO supplies to the FPGA can

be applied in any order if this requirement is met. However, an external configuration source might have specific requirements. Check the

data sheet for the attached configuration source. Apply VCCINT last for lowest overall power consumption (see the chapter called “Powering

Spartan-3 Generation FPGAs” in UG331 for more information).

2.

To ensure successful power-on, VCCINT, VCCO Bank 2, and VCCAUX supplies must rise through their respective threshold-voltage ranges with

no dips at any point.

Table 9: Supply Voltage Levels Necessary for Preserving CMOS Configuration Latch (CCL) Contents and RAM Data

Symbol

Description

Min

Units

VDRINT

VCCINT level required to retain CMOS Configuration Latch (CCL) and RAM data

1.0

V

VDRAUX

VCCAUX level required to retain CMOS Configuration Latch (CCL) and RAM data

2.0

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3SD1800A-4CSG484LI | IC FPGA SPARTAN 3 DSP 484CSGBGA |

| XC3SD3400A-4FGG676I | SPARTAN-3ADSP FPGA 3400K 676FBGA |

| XC4036XLA-09HQ240C | IC FPGA C 2.5V 288 I/O 240HQFP |

| XC4062XL-09HQ240C | IC FPGA C-TEMP 3.3V 240-HQFP |

| XC4085XL-3BG560I | IC FPGA I-TEMP 3.3V 3SPD 560MBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S400AN-4FG400I4100 | 制造商:Xilinx 功能描述: |

| XC3S400AN-4FGG400C | 功能描述:IC SPARTAN-3AN FPGA 400K 400FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3AN 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S400AN-4FGG400CES | 制造商:Xilinx 功能描述: |

| XC3S400AN-4FGG400I | 功能描述:IC FPGA SPARTAN-3A 400K 400-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3AN 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S400AN-4FT256C | 制造商:Xilinx 功能描述:SPARTAN3AN - Trays 制造商:Xilinx 功能描述:IC FPGA SPARTAN-3AN 400K 256BGA 制造商:Xilinx 功能描述:IC FPGA 195 I/O 256FTBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。