- 您現在的位置:買賣IC網 > PDF目錄16526 > XR16M2752IJ-0B-EB (Exar Corporation)EVAL BOARD FOR M2752-B 44PLCC PDF資料下載

參數資料

| 型號: | XR16M2752IJ-0B-EB |

| 廠商: | Exar Corporation |

| 文件頁數: | 23/51頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR M2752-B 44PLCC |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

XR16M2752

3

REV. 1.0.0

1.62V TO 3.63V HIGH PERFORMANCE DUART WITH 64-BYTE FIFO

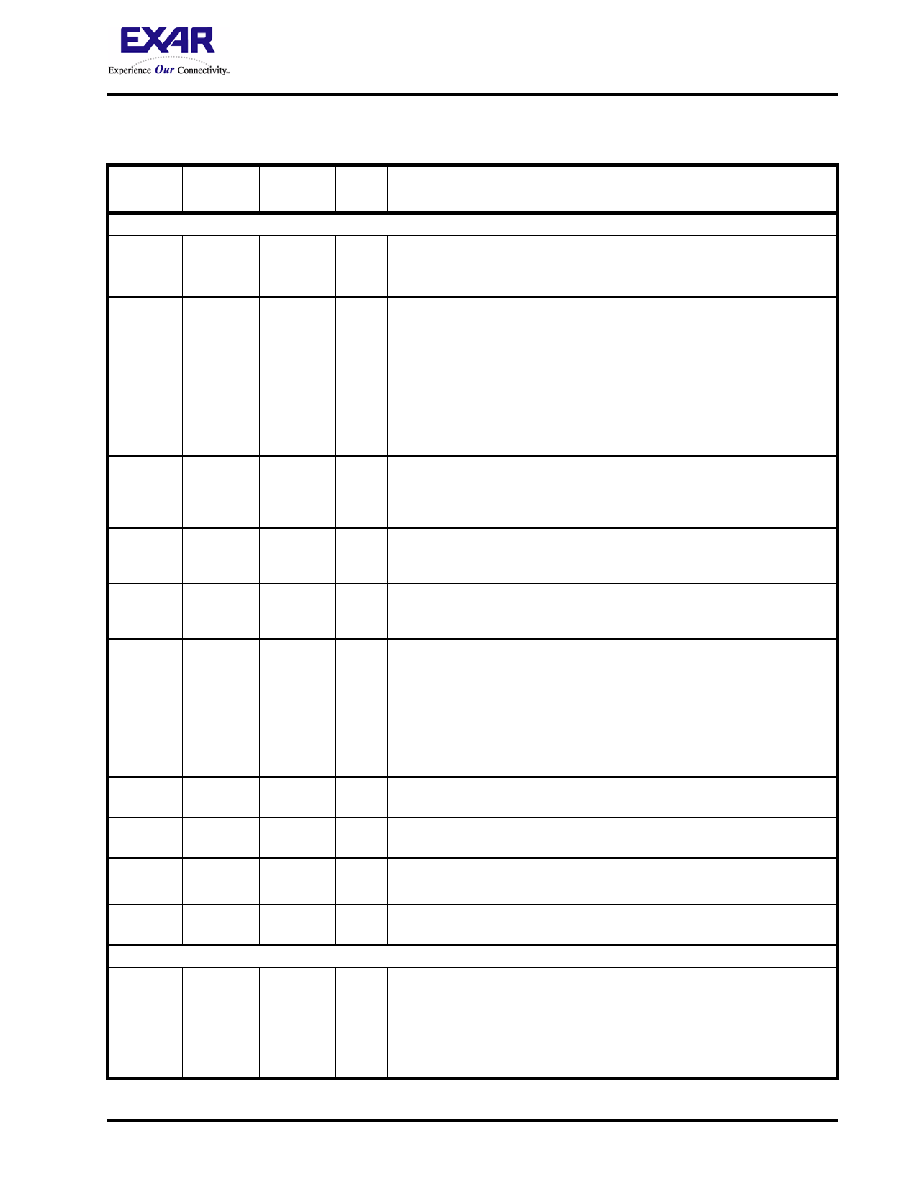

PIN DESCRIPTIONS

Pin Description

NAME

32-QFN

PIN #

44-PLCC

PIN #

TYPE

DESCRIPTION

DATA BUS INTERFACE

A2

A1

A0

7

6

3

15

14

10

I

Address data lines [2:0]. These 3 address lines select one of the internal

registers in UART channel A/B during a data bus transaction.

D7

D6

D5

D4

D3

D2

D1

D0

2

1

32

31

30

29

28

27

9

8

7

6

5

4

3

2

I/O

Data bus lines [7:0] (bidirectional).

IOR#

14

24

I

Input/Output Read Strobe (active low). The falling edge instigates an inter-

nal read cycle and retrieves the data byte from an internal register pointed

to by the address lines [A2:A0]. The data byte is placed on the data bus to

allow the host processor to read it on the rising edge.

IOW#

11

20

I

Input/Output Write Strobe (active low). The falling edge instigates an inter-

nal write cycle and the rising edge transfers the data byte on the data bus

to an internal register pointed by the address lines.

CS#

10

18

I

UART chip select (active low). This function selects channel A or B in

accordance with the logical state of the CHSEL pin. This allows data to be

transferred between the user CPU and the 2752.

CHSEL

8

16

I

Channel Select - UART channel A or B is selected by the logical state of

this pin when the CS# pin is a logic 0. A logic 0 on the CHSEL selects the

UART channel B while a logic 1 selects UART channel A. Normally,

CHSEL could just be an address line from the user CPU such as A4. Bit-0

of the Alternate Function Register (AFR) can temporarily override CHSEL

function, allowing the user to write to both channel register simultaneously

with one write cycle when CS# is low. It is especially useful during the ini-

tialization routine.

INTA

21

34

O

UART channel A Interrupt output (active high). A logic high indicates chan-

nel A is requesting for service. For more details, see

INTB

9

17

O

UART channel B Interrupt output (active high). A logic high indicates chan-

nel B is requesting for service. For more details, see

TXRDYA#

-

1

O

UART channel A Transmitter Ready (active low). The output provides the

TX FIFO/THR status for transmit channel A. See

TXRDYB#

-

32

O

UART channel B Transmitter Ready (active low). The output provides the

TX FIFO/THR status for transmit channel B.

See Table 2.

MODEM OR SERIAL I/O INTERFACE

TXA

23

38

O

UART channel A Transmit Data or infrared encoder data. Standard trans-

mit and receive interface is enabled when MCR[6] = 0. In this mode, the

TX signal will be HIGH during reset or idle (no data). Infrared IrDA transmit

and receive interface is enabled when MCR[6] = 1. In the Infrared mode,

the inactive state (no data) for the Infrared encoder/decoder interface is

LOW. If it is not used, leave it unconnected.

相關PDF資料 |

PDF描述 |

|---|---|

| AQ1055N1S-T | INDUCTOR 5.1NH 460MA 0402 SMD |

| VE-J0F-EZ-S | CONVERTER MOD DC/DC 72V 25W |

| 1-5504970-2 | CA 62.5/125UMLDS SC TO SC |

| H8MMH-4036M | DIP CABLE - HDM40H/AE40M/HDM40H |

| VE-JTF-EZ-S | CONVERTER MOD DC/DC 72V 25W |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR16M2752IJ44 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16M2752IJ44-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M2752IL-0A-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M2752IL-0A RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M2752IL-0B-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M2752IL Series RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M2752IL32 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復。