- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄16433 > XR17C154CV-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17C154-A 144TQF PDF資料下載

參數(shù)資料

| 型號(hào): | XR17C154CV-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 5/62頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR17C154-A 144TQF |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

xr

XR17C154

REV. 1.3.2

5V PCI BUS QUAD UART

13

1.2.1

The Interrupt Status Register

The XR17C154 has a 32-bit wide register [INT0, INT1, INT2 and INT3] to provide interrupt information and

supports two interrupt schemes. The first scheme uses bits 0 to 3 of an 8-bit indicator (INT0) representing

channels 0 to 3 of the XR17C154, respectively. This permits the interrupt routine to quickly vector and serve

that UART channel and determine the source(s) in each individual routines. INT0 bit-0 represents the interrupt

status for UART channel 0 when its transmitter, receiver, line status, or modem port status requires service.

Other bits in the INT0 register provide indication for the other channels with bit-3 representing UART channel 3

respectively. Bits 4 through 7 are reserved and remain at a logic 0.

The second scheme provides detail about the source of the interrupts for each UART channel. All the interrupts

are encoded into a 3-bit code. This 3-bit code represents 7 interrupts corresponding to individual UART’s

transmitter, receiver, line status, modem port status. INT1 and INT2 registers provide the 12-bit interrupt status

for all 4 channels. Bits 8, 9 and 10 representing channel 0 and bits 17, 18 and 19 representing channel 3

respectively. Bits 20 to 31 are reserved and remain at a logic 0. All 4 channel interrupts status are available

with a single DWORD read operation. This feature allows the host quickly vectors and serves the interrupts,

reducing service interval, hence, reduce host bandwidth requirement. Figure 4 shows the 4-byte interrupt

register and its make up.

A special interrupt condition is generated by the 154 when it wakes up from sleep mode. This special interrupt

is cleared by reading the INT0 register. If there are not any other interrupts pending, the value read from INT0

would be 0x00.

INT0 [7:0] Channel Interrupt Indicator

Each bit gives an indication of the channel that has requested for service. Bit-0 represents channel 0 and bit-3

indicates channel 3. Logic 1 indicates that a channel has called for service. Bits 4 to 7 are reserved and remain

at a logic 0. The interrupt bit clears after reading the appropriate register of the interrupting channel register,

see Interrupt Clearing section.

INT3, INT2 and INT1 [32:8]

Twenty four bit encoded interrupt indicator. Each channel’s interrupt is encoded into 3 bits for receive, transmit,

and status. Bit [10:8] represent channel 0 and go up to channel 3 with bits [19:17]. The 3 bit encoding and their

priority order are shown below in Table 5. The Timer and MPIO interrupts are for the device and therefore they

exist within channel 0 space (bits [10:8]) and not in other channel.

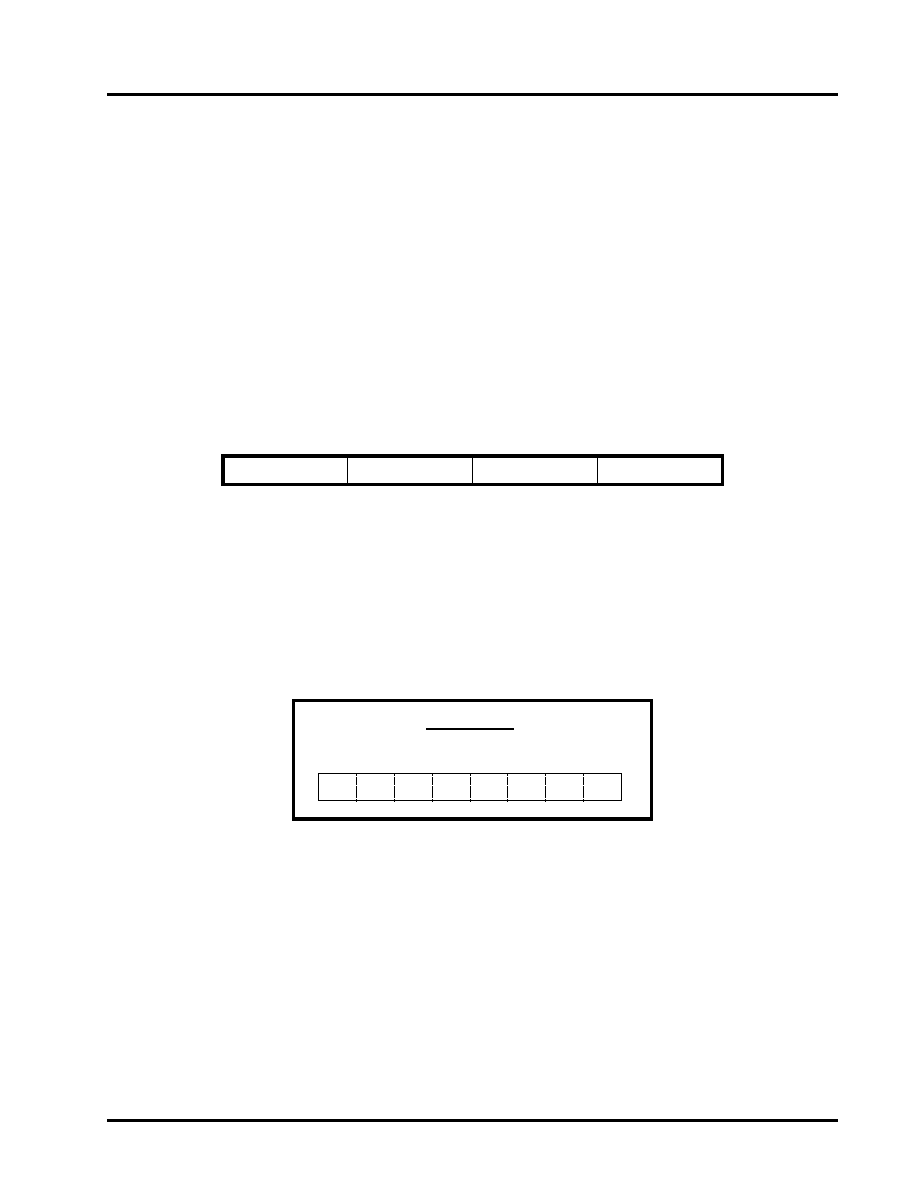

GLOBAL INTERRUPT REGISTER (DWORD)

[default 0x00-00-00-00]

INT3 [31:24]

INT2 [23:16]

INT1 [15:8]

INT0 [7:0]

The INT0 register provides individual status for each channel

INT0 Register

Individual UART Channel Interrupt Status

Rsvd

Ch-3 Ch-2 Ch-1 Ch-0

Bit-7 Bit-6 Bit-5 Bit-4 Bit-3 Bit-2 Bit-1 Bit-0

Rsvd Rsvd Rsvd

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR16V798IQ-0B-EVB | EVAL BOARD FOR XR16V798-B 100QFP |

| XR16V798IQ-0A-EVB | EVAL BOARD FOR XR16V798-A 100QFP |

| XR16V698IQ-0B-EVB | EVAL BOARD FOR XR16V698-B 100QFP |

| XR16V698IQ-0A-EVB | EVAL BOARD FOR XR16V698-A 100QFP |

| KIT33972AEWEVBE | KIT EVALUATION FOR MC33972 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17C154CV-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C154CVTR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17C154CVTR-F |

| XR17C154IV | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C154IV-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C154IVTR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17C154IVTR-F |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。