- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16433 > XR17D154CV-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17D154 144TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XR17D154CV-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 5/69頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR17D154 144TQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

xr

XR17D154

REV. 1.2.2

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

13

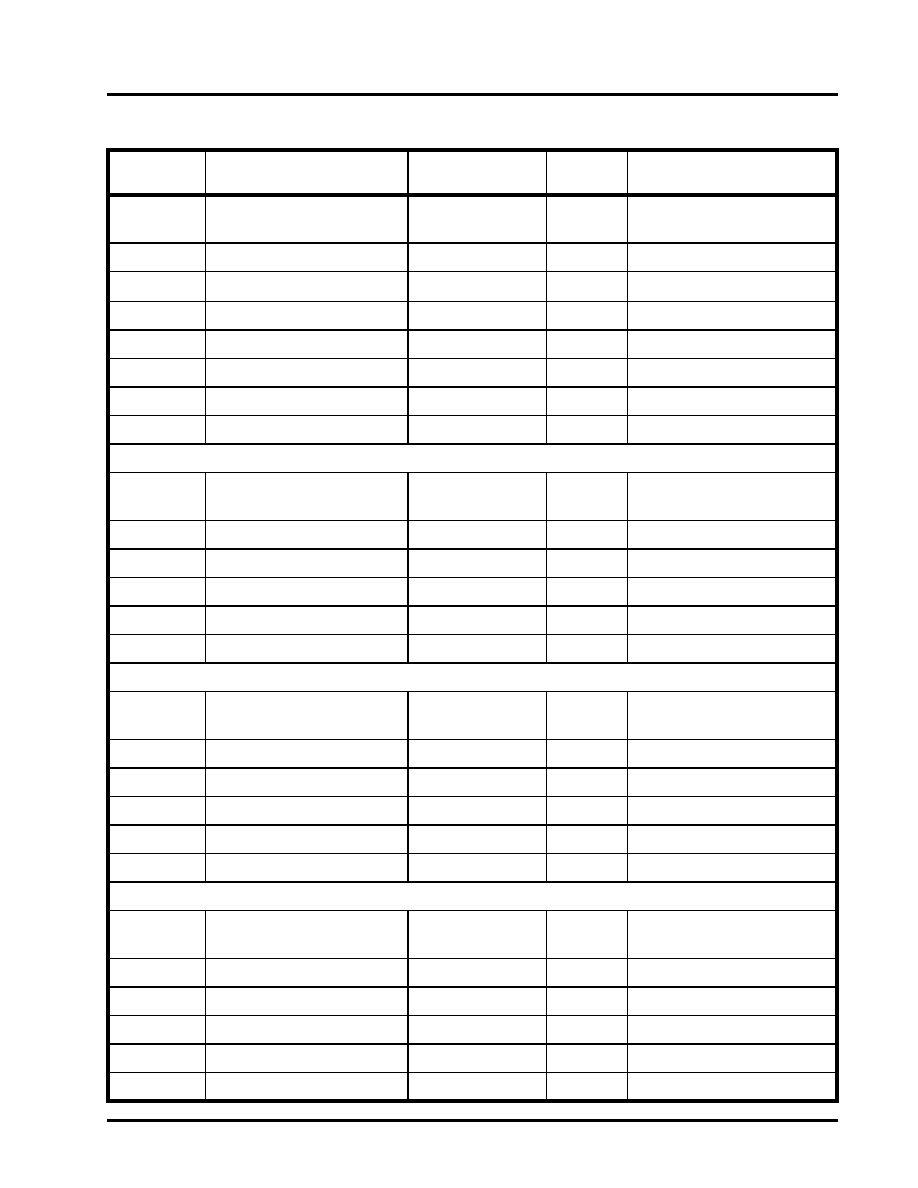

TABLE 3: XR17D154 DEVICE CONFIGURATION REGISTERS

OFFSET

ADDRESS

MEMORY SPACE

READ/WRITE

DATA WIDTH

COMMENT

0x000 - 0x00F UART channel 0 Regs

(

Table 12 &

8/16/24/32 First 8 regs are 16550 compatible

0x010 - 0x07F Reserved

0x080 - 0x093 DEVICE CONFIG. REGISTERS

(

8/16/24/32

0x094 - 0x0FF Reserved

Read/Write

0x100 - 0x13F UART 0 – Read FIFO

Read-Only

8/16/24/32 64 bytes of RX FIFO data

0x100 - 0x13F UART 0 – Write FIFO

Write-Only

8/16/24/32 64 bytes of TX FIFO data

0x140 - 0x17F Reserved

0x180 - 0x1FF UART 0 – Read FIFO with errors

Read-Only

16/32

64 bytes of RX FIFO data + LSR

0x200 - 0x20F UART channel 1 Regs

(

Table 12 &

8/16//24/32 First 8 regs are 16550 compatible

0x210 - 0x2FF Reserved

Read/Write

0x300 - 0x33F UART 1 – Read FIFO

Read-Only

8/16/24/32 64 bytes of RX FIFO data

0x300 - 0x33F UART 1 – Write FIFO

Write-Only

8/16/24/32 64 bytes of TX FIFO data

0x340 - 0x37F Reserved

0x380 - 0x3FF UART 1 – Read FIFO with errors

Read-Only

16/32

64 bytes of RX FIFO data + LSR

0x400 - 0x40F UART channel 2 Regs

(

Table 12 &

8/16/24/32 First 8 regs are 16550 compatible

0x410 - 0x4FF Reserved

Read/Write

0x500 - 0x53F UART 2 – Read FIFO

Read-Only

8/16/24/32 64 bytes of RX FIFO data

0x500 - 0x53F UART 2 – Write FIFO

Write-Only

8/16/24/32 64 bytes of TX FIFO data

0x540 - 0x57F Reserved

0x580 - 0x5FF UART 2 – Read FIFO with errors

Read-Only

16/32

64 bytes of RX FIFO data + LSR

0x600 - 0x60F UART channel 3 Regs

(

Table 12 &

8/16/24/32 First 8 regs are 16550 compatible

0x610 - 0x6FF Reserved

Read/Write

0x700 - 0x73F UART 3 – Read FIFO

Read-Only

8/16/24/32 64 bytes of RX FIFO data

0x700 - 0x73F UART 3 – Write FIFO

Write-Only

8/16/24/32 64 bytes of TX FIFO data

0x740 - 0x77F Reserved

0x780 - 0x7FF UART 3 – Read FIFO with errors

Read-Only

16/32

64 bytes of RX FIFO data + LSR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ECM22DCST | CONN EDGECARD 44POS DIP .156 SLD |

| 5349565-9 | FOMM50 LEAD 2.5 TZ SC/PC-SC/PC |

| CM322522-R22ML | INDUCTOR 220NH 360MA SMD |

| 2-6374659-0 | C/A LC TO LC MM 2.0MM 20M1 |

| CDRH125/LDNP-330MC | POWER INDUCTOR 33UH 2.6A SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17D154CV-F | 功能描述:UART 接口集成電路 3.3V-5V 64B FIFO temp 0C to 70C; UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17D154CVTR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 3.3V/5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D154CVTR-F |

| XR17D154IV | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17D154IV-F | 功能描述:UART 接口集成電路 3.3V-5V 64B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17D154IVTR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 3.3V/5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D154IVTR-F |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。