- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16428 > XR17V254IV-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17V254 144LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XR17V254IV-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 5/70頁(yè) |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V254 144LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)

XR17V254

13

REV. 1.0.1

66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT

1.4

EEPROM Interface

The V254 provides an interface to an Electrically Erasable Programmable Read Only Memory (EEPROM). The

EEPROM must be a 93C46-like device, with its memory configured as 16-bit words. This interface is provided

in order to program the registers in the PCI Configuration Space of the PCI UART during power-up. The

following table gives the mapping of the EEPROM memory to the registers in the V254’s PCI Configuration

Space. When the PCI RST# is negated, the V254 will download the data from the EEPROM, if it detects a

HIGH on the EECS pin. The V254 takes a maximum of 216 PCI clocks from the rising edge of the PCI RST#

signal to read the EEPROM data. For more details on the EEPROM interface, please refer to the application

note DAN112 on Exar’s website.

NOTE: * Only the upper 8 bits in this word in EEPROM location are used and the lower 8 bits are ignored. The lower byte at

PCI Config space 0x08 is Device Revision and is read-only.

1.5

Device Internal Register Sets

The Device Configuration Registers and the four individual UART Configuration Registers of the V254

occupy 2K of PCI bus memory address space. These addresses are offset onto the basic memory address, a

value loaded into the Memory Base Address Register (BAR) in the PCI local bus configuration register set. The

UART Configuration Registers are mapped into 4 address blocks where each UART channel occupies 512

bytes memory space for its own registers that include the 16550 compatible registers. The Device

Configuration Registers are embedded inside the UART channel zero’s address space between 0x0080 to

0x0093. All these registers can be accessed in 8, 16, 24 or 32 bits width depending on the starting address

given by the host at beginning of the bus cycle. Transmit and receive data may be loaded or unloaded in 8, 16,

24 or 32 bits format in special locations given in the Table 5 below. Every time a read or write operation is

made to the transmit or receive register, its FIFO data pointer is automatically bumped to the next sequential

data location either in byte, word or dword. One special case applies to the receive data unloading when

reading the receive data together with its LSR register content. The host must read them in 16 or 32 bits format

in order to maintain integrity of the data byte with its associated error flags. These special registers are further

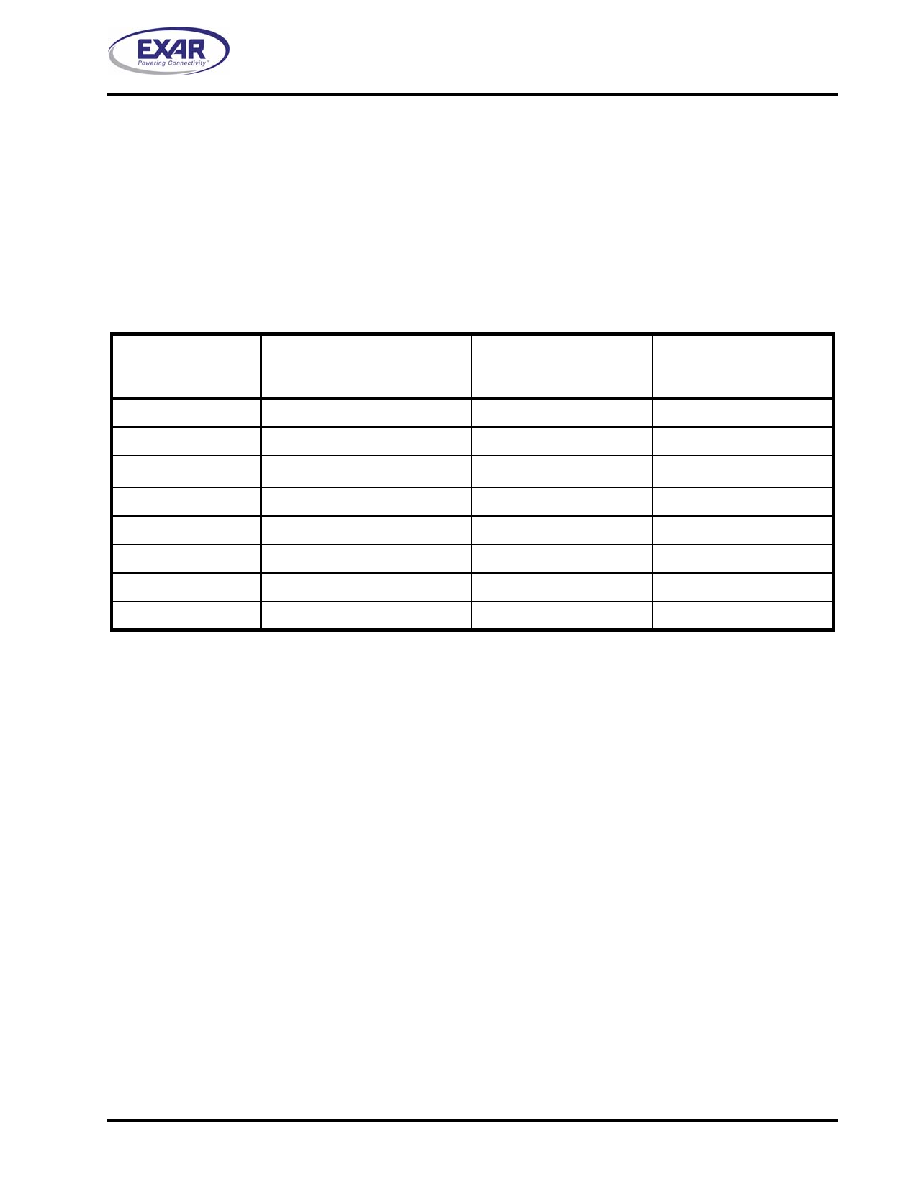

TABLE 4: EEPROM ADDRESS DEFINITIONS

EEPROM MEMORY

ADDRESS

EEPROM DATA [D15:D0]

V254’S PCI CONFIGURATION

SPACE ADDRESS

(WORD OFFSET)

DEFAULT VALUES

0x00

Vendor ID

0x00

0x13A8

0x01

Device ID

0x02

0x0254

0x02

Class Code*

0x08

0x0200

0x03

Class Code (Continued)

0x0A

0x0700

0x04

Subsystem Vendor ID

0x2C

0x0000

0x05

Subsystem ID

0x2E

0x0000

0x06

Special Register (Lower Word)

0x48

0x0000

0x07

Special Register (Upper Word)

0x4A

0x0000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RPS0J102MCN1GS | CAP ALUM 1000UF 6.3V 20% SMD |

| EMM10DRMN | CONN EDGECARD 20POS .156 WW |

| GBA31DRMN-S288 | CONN EDGECARD 62POS .125 EXTEND |

| CM100505-18NGL | INDUCTOR CHIP 18NH 1005 SMD |

| 1-6828247-5 | CA,SM,MTRJ-SC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17V254IV-F | 功能描述:UART 接口集成電路 66MHz Quad PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT |

| XR17V258_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT |

| XR17V258IV | 功能描述:UART 接口集成電路 66MHz Octal PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258IV-0A-EVB | 功能描述:UART 接口集成電路 Supports V258 144 ld TQFP, PCI Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。