- 您現在的位置:買賣IC網 > PDF目錄16821 > XR17V354IB-E8-EVB (Exar Corporation)EVAL BRD FOR XR17V354-E8 176BGA PDF資料下載

參數資料

| 型號: | XR17V354IB-E8-EVB |

| 廠商: | Exar Corporation |

| 文件頁數: | 66/66頁 |

| 文件大小: | 0K |

| 描述: | EVAL BRD FOR XR17V354-E8 176BGA |

| 產品培訓模塊: | PCIe UARTs |

| 標準包裝: | 1 |

| 主要目的: | 接口,UART |

| 嵌入式: | 否 |

| 已用 IC / 零件: | XR17V354 |

| 已供物品: | 板 |

| 其它名稱: | 1016-1613 XR17V354IB-E8-EVB-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當前第66頁

XR17V354

9

REV. 1.0.3

HIGH PERFORMANCE QUAD PCI-EXPRESS UART

1.0 XR17V354 INTERNAL REGISTERS

The XR17V354 UART register set is very similar to the previous generation PCI UARTs. This makes the V354

software compatible with the previous generation PCI UARTs. Minimal changes are needed to the software

driver of an existing Exar PCI UART driver so that it can be used with the V354 PCIe UART.

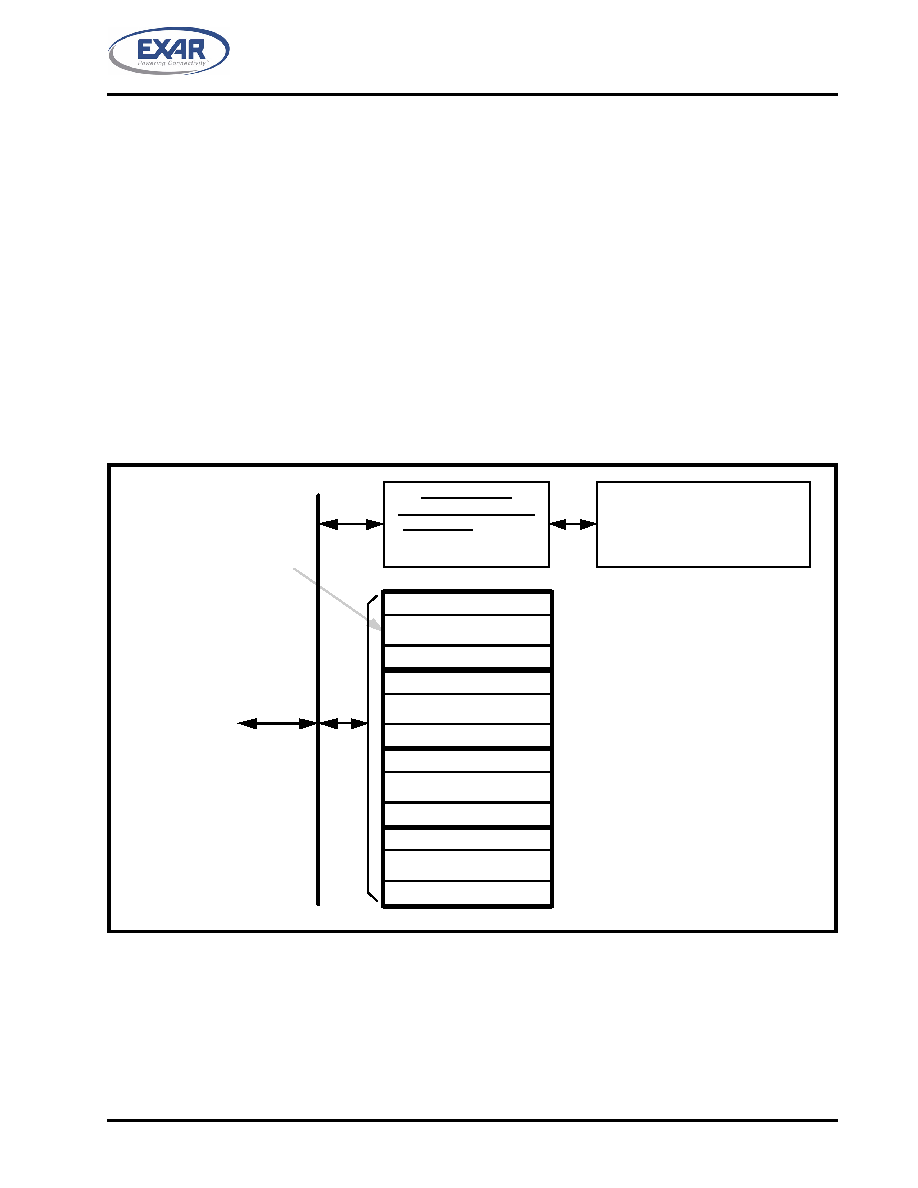

There are three different sets of registers as shown in Figure 3. The PCI Local Bus Configuration Space

Registers is needed for plug-and-play auto-configuration. This auto-configuration feature makes installation

very easy into a PCI system and it is part of the PCI local bus specification. The second register set is the

Device Configuration Registers that are also accessible directly from the PCI bus for programming general

operating conditions of the device and monitoring the status of various functions common to all four channels.

These functions include all 4 channel UARTs’ interrupt control and status, 16-bit general purpose timer control

and status, multipurpose inputs/outputs control and status, sleep mode, soft-reset, and device identification

and revision. And lastly, each UART channel has its own set of internal UART Configuration Registers for its

own operation control and status reporting. All 4 sets of channel registers are embedded inside the device

configuration registers space, which provides faster access. The second and third set of registers are mapped

into 4K of the PCI bus memory address space. The following paragraphs describe all 3 sets of registers in

detail.

FIGURE 3. THE XR17V354 REGISTER SETS

Channel 0 16550 com patible

registers + enhanced registers

Device Configuration Registers

Device Configuration and

UART[3:0] Configuration

Registers are m apped on

to the Base Address

Register (BAR ) in a 4K-

byte of m em ory address

space

PCIe

Interface

Channel 0 TX FIFO , R X FIFO ,

RX FIFO + Status Burst R eg

PCI Local Bus

Configuration Space

Registers for Plug-

and-Play Auto

Configuration

Vendor and Sub-vendor ID

and Product M odel Num ber

in External EEPRO M

0x0000

0x0400

0x0800

0x0C00

0x0FFF

0x0080

0x0100

Device Configuration Registers

Channel 1 16550 com patible

registers + enhanced registers

Channel 1 TX FIFO , R X FIFO ,

RX FIFO + Status Burst R eg

Channel 2 TX FIFO , R X FIFO ,

RX FIFO + Status Burst R eg

Channel 3 TX FIFO , R X FIFO ,

RX FIFO + Status Burst R eg

Channel 2 16550 com patible

registers + enhanced registers

Channel 3 16550 com patible

registers + enhanced registers

1.1

PCI LOCAL BUS CONFIGURATION SPACE REGISTERS

The PCI local bus configuration space registers are responsible for setting up the device’s operating

environment in the PCI local bus. The pre-defined operating parameters of the device is read by the PCI bus

plug-and-play auto-configuration manager in the operating system. After the PCI bus has collected all data

from every device/card on the bus, it defines and downloads the memory mapping information to each device/

card about their individual operation memory address location and conditions. The operating memory mapped

address location is downloaded into the Base Address Register (BAR) register, located at an address offset of

0x10 in the configuration space. Custom modification of certain registers is possible by using an external

相關PDF資料 |

PDF描述 |

|---|---|

| V150B28E150B2 | CONVERTER MOD DC/DC 28V 150W |

| EBM25DRMD | CONN EDGECARD 50POS .156 WW |

| RPS0J820MCN1GS | CAP ALUM 82UF 6.3V 20% SMD |

| H8PPS-2406G | DIP CABLE - HDP24S/AE24G/HDP24S |

| XR17V354IB-E4-EVB | EVAL BRD FOR XR17V354-E4 176BGA |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR17V358 | 制造商:EXAR 制造商全稱:EXAR 功能描述:HIGH PERFORMANCE OCTAL PCI EXPRESS UART |

| XR17V358IB-0A-EVB | 功能描述:界面開發(fā)工具 Eval Board for XR17V358IB-0A RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR17V358IB176-F | 功能描述:UART 接口集成電路 8 Channel PCIe UART w/256 Byte FIFO RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V358IB176-F | 制造商:Exar Corporation 功能描述:IC OCTAL UART 25MBPS 3.6V 176-BGA |

| XR17V358IB-E4-EVB | 功能描述:界面開發(fā)工具 Eval Board for XR17V358IB-E4 RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。