- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗1976 > XRT72L52IQTR-F (Exar Corporation)IC FRAMER DS3/E3 2CH 160QFP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉锛� | XRT72L52IQTR-F |

| 寤犲晢锛� | Exar Corporation |

| 鏂囦欢闋佹暩(sh霉)锛� | 126/488闋� |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC FRAMER DS3/E3 2CH 160QFP |

| 鐢�(ch菐n)鍝佽畩鍖栭€氬憡锛� | XRT72Lx Series Obsolescence 02/May/2012 |

| 妯欐簴鍖呰锛� | 250 |

| 鎺у埗鍣ㄩ鍨嬶細 | DS3/E3 瑾�(di脿o)骞€鍣� |

| 闆绘簮闆诲锛� | 3.3V |

| 闆绘祦 - 闆绘簮锛� | 100mA |

| 宸ヤ綔婧害锛� | -40°C ~ 85°C |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 灏佽/澶栨锛� | 160-BQFP |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 160-PQFP锛�28x28锛� |

| 鍖呰锛� | 甯跺嵎 (TR) |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�绗�26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�绗�35闋�绗�36闋�绗�37闋�绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�绗�43闋�绗�44闋�绗�45闋�绗�46闋�绗�47闋�绗�48闋�绗�49闋�绗�50闋�绗�51闋�绗�52闋�绗�53闋�绗�54闋�绗�55闋�绗�56闋�绗�57闋�绗�58闋�绗�59闋�绗�60闋�绗�61闋�绗�62闋�绗�63闋�绗�64闋�绗�65闋�绗�66闋�绗�67闋�绗�68闋�绗�69闋�绗�70闋�绗�71闋�绗�72闋�绗�73闋�绗�74闋�绗�75闋�绗�76闋�绗�77闋�绗�78闋�绗�79闋�绗�80闋�绗�81闋�绗�82闋�绗�83闋�绗�84闋�绗�85闋�绗�86闋�绗�87闋�绗�88闋�绗�89闋�绗�90闋�绗�91闋�绗�92闋�绗�93闋�绗�94闋�绗�95闋�绗�96闋�绗�97闋�绗�98闋�绗�99闋�绗�100闋�绗�101闋�绗�102闋�绗�103闋�绗�104闋�绗�105闋�绗�106闋�绗�107闋�绗�108闋�绗�109闋�绗�110闋�绗�111闋�绗�112闋�绗�113闋�绗�114闋�绗�115闋�绗�116闋�绗�117闋�绗�118闋�绗�119闋�绗�120闋�绗�121闋�绗�122闋�绗�123闋�绗�124闋�绗�125闋�鐣跺墠绗�126闋�绗�127闋�绗�128闋�绗�129闋�绗�130闋�绗�131闋�绗�132闋�绗�133闋�绗�134闋�绗�135闋�绗�136闋�绗�137闋�绗�138闋�绗�139闋�绗�140闋�绗�141闋�绗�142闋�绗�143闋�绗�144闋�绗�145闋�绗�146闋�绗�147闋�绗�148闋�绗�149闋�绗�150闋�绗�151闋�绗�152闋�绗�153闋�绗�154闋�绗�155闋�绗�156闋�绗�157闋�绗�158闋�绗�159闋�绗�160闋�绗�161闋�绗�162闋�绗�163闋�绗�164闋�绗�165闋�绗�166闋�绗�167闋�绗�168闋�绗�169闋�绗�170闋�绗�171闋�绗�172闋�绗�173闋�绗�174闋�绗�175闋�绗�176闋�绗�177闋�绗�178闋�绗�179闋�绗�180闋�绗�181闋�绗�182闋�绗�183闋�绗�184闋�绗�185闋�绗�186闋�绗�187闋�绗�188闋�绗�189闋�绗�190闋�绗�191闋�绗�192闋�绗�193闋�绗�194闋�绗�195闋�绗�196闋�绗�197闋�绗�198闋�绗�199闋�绗�200闋�绗�201闋�绗�202闋�绗�203闋�绗�204闋�绗�205闋�绗�206闋�绗�207闋�绗�208闋�绗�209闋�绗�210闋�绗�211闋�绗�212闋�绗�213闋�绗�214闋�绗�215闋�绗�216闋�绗�217闋�绗�218闋�绗�219闋�绗�220闋�绗�221闋�绗�222闋�绗�223闋�绗�224闋�绗�225闋�绗�226闋�绗�227闋�绗�228闋�绗�229闋�绗�230闋�绗�231闋�绗�232闋�绗�233闋�绗�234闋�绗�235闋�绗�236闋�绗�237闋�绗�238闋�绗�239闋�绗�240闋�绗�241闋�绗�242闋�绗�243闋�绗�244闋�绗�245闋�绗�246闋�绗�247闋�绗�248闋�绗�249闋�绗�250闋�绗�251闋�绗�252闋�绗�253闋�绗�254闋�绗�255闋�绗�256闋�绗�257闋�绗�258闋�绗�259闋�绗�260闋�绗�261闋�绗�262闋�绗�263闋�绗�264闋�绗�265闋�绗�266闋�绗�267闋�绗�268闋�绗�269闋�绗�270闋�绗�271闋�绗�272闋�绗�273闋�绗�274闋�绗�275闋�绗�276闋�绗�277闋�绗�278闋�绗�279闋�绗�280闋�绗�281闋�绗�282闋�绗�283闋�绗�284闋�绗�285闋�绗�286闋�绗�287闋�绗�288闋�绗�289闋�绗�290闋�绗�291闋�绗�292闋�绗�293闋�绗�294闋�绗�295闋�绗�296闋�绗�297闋�绗�298闋�绗�299闋�绗�300闋�绗�301闋�绗�302闋�绗�303闋�绗�304闋�绗�305闋�绗�306闋�绗�307闋�绗�308闋�绗�309闋�绗�310闋�绗�311闋�绗�312闋�绗�313闋�绗�314闋�绗�315闋�绗�316闋�绗�317闋�绗�318闋�绗�319闋�绗�320闋�绗�321闋�绗�322闋�绗�323闋�绗�324闋�绗�325闋�绗�326闋�绗�327闋�绗�328闋�绗�329闋�绗�330闋�绗�331闋�绗�332闋�绗�333闋�绗�334闋�绗�335闋�绗�336闋�绗�337闋�绗�338闋�绗�339闋�绗�340闋�绗�341闋�绗�342闋�绗�343闋�绗�344闋�绗�345闋�绗�346闋�绗�347闋�绗�348闋�绗�349闋�绗�350闋�绗�351闋�绗�352闋�绗�353闋�绗�354闋�绗�355闋�绗�356闋�绗�357闋�绗�358闋�绗�359闋�绗�360闋�绗�361闋�绗�362闋�绗�363闋�绗�364闋�绗�365闋�绗�366闋�绗�367闋�绗�368闋�绗�369闋�绗�370闋�绗�371闋�绗�372闋�绗�373闋�绗�374闋�绗�375闋�绗�376闋�绗�377闋�绗�378闋�绗�379闋�绗�380闋�绗�381闋�绗�382闋�绗�383闋�绗�384闋�绗�385闋�绗�386闋�绗�387闋�绗�388闋�绗�389闋�绗�390闋�绗�391闋�绗�392闋�绗�393闋�绗�394闋�绗�395闋�绗�396闋�绗�397闋�绗�398闋�绗�399闋�绗�400闋�绗�401闋�绗�402闋�绗�403闋�绗�404闋�绗�405闋�绗�406闋�绗�407闋�绗�408闋�绗�409闋�绗�410闋�绗�411闋�绗�412闋�绗�413闋�绗�414闋�绗�415闋�绗�416闋�绗�417闋�绗�418闋�绗�419闋�绗�420闋�绗�421闋�绗�422闋�绗�423闋�绗�424闋�绗�425闋�绗�426闋�绗�427闋�绗�428闋�绗�429闋�绗�430闋�绗�431闋�绗�432闋�绗�433闋�绗�434闋�绗�435闋�绗�436闋�绗�437闋�绗�438闋�绗�439闋�绗�440闋�绗�441闋�绗�442闋�绗�443闋�绗�444闋�绗�445闋�绗�446闋�绗�447闋�绗�448闋�绗�449闋�绗�450闋�绗�451闋�绗�452闋�绗�453闋�绗�454闋�绗�455闋�绗�456闋�绗�457闋�绗�458闋�绗�459闋�绗�460闋�绗�461闋�绗�462闋�绗�463闋�绗�464闋�绗�465闋�绗�466闋�绗�467闋�绗�468闋�绗�469闋�绗�470闋�绗�471闋�绗�472闋�绗�473闋�绗�474闋�绗�475闋�绗�476闋�绗�477闋�绗�478闋�绗�479闋�绗�480闋�绗�481闋�绗�482闋�绗�483闋�绗�484闋�绗�485闋�绗�486闋�绗�487闋�绗�488闋�

XRT72L52

195

REV. 1.0.3

TWO CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

NOTES:

1.

The default condition is the Bipolar Mode.

2.

This selection also effects the Transmit DS3 Framer Line Interface Output Mode

4.3.1.2

Bipolar Decoding

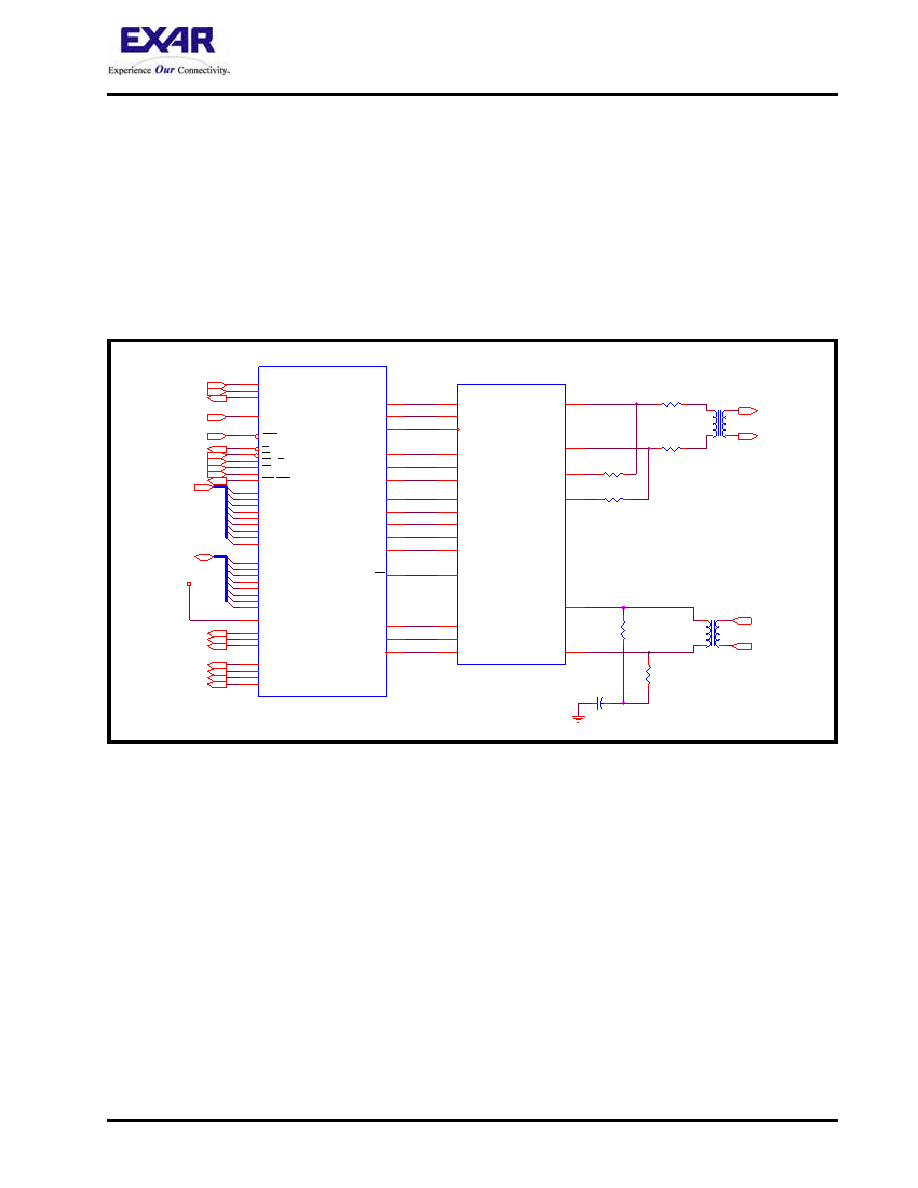

If the Receive DS3 LIU Interface block is operating in the Bipolar Mode, then it will receive the DS3 data pulses

via both the RxPOS, RxNEG, and the RxLineClk input pins. Figure 62 presents a circuit diagram illustrating

how the Receive DS3 LIU Interface block interfaces to the Line Interface Unit while the Framer is operating in

Bipolar mode. The Receive DS3 LIU Interface block can be configured to decode the incoming data from

either the AMI or B3ZS line codes.

4.3.1.2.1

AMI Decoding

AMI or Alternate Mark Inversion, means that consecutive one's pulses (or marks) will be of opposite polarity

with respect to each other. This line code involves the use of three different amplitude levels: +1, 0, and -1.

The +1 and -1 amplitude signals are used to represent one's (or mark) pulses and the "0" amplitude pulses (or

the absence of a pulse) are used to represent zeros (or space) pulses. The general rule for the AMI line code

is: if a given mark pulse is of positive polarity, then the very next mark pulse will be of negative polarity and vice

versa. This alternating-polarity relationship exists between two consecutive mark pulses, independent of the

number of zeros that exist between these two pulses. Figure 63 presents an illustration of the AMI Line Code

as would appear at the RxPOS and RxNEG input pins of the Framer, as well as the corresponding output

signal on the line.

FIGURE 62. IINTERFACING THE XRT72L52 FRAMER IC TO THE XRT73L00 DS3/E3/STS-1 LIU

VDD

U1

XRT72L50

TxPOS

65

TxNEG

64

TxLineClk

63

DMO

79

ExtLOS

78

RLOL

77

LLOOP

69

RLOOP

70

TAOS

68

TxLev

67

EncoDis

66

Req

71

RxPOS

76

RxNEG

75

RxLineClk

74

MOTO

27

Reset

28

A0

15

A1

16

A2

17

A3

18

A4

19

A5

20

A6

21

A7

22

A8

23

D0

32

D1

33

D2

34

D3

35

D4

36

D5

37

D6

38

D7

39

RDY_DTCK

6

WR_R/W

7

RD_DS

10

CS

8

ALE_AS

9

Int

13

TxSer/SndMsg

45

TxInClk

43

TxFrame

61

RxSer/RxIdle

86

RxClk

88

RxFrame

90

RxLOS

95

RxOOF

94

RxRed

93

RxAIS

87

NibIntf

25

U2

XRT73L00

TPDATA

37

TNDATA

38

TCLK

36

RCLK1

31

RNEG

32

RPOS

33

TTIP

41

TRING

40

MTIP

44

MRING

43

RRING

9

RTIP

8

DMO

4

RLOS

24

RLOL

23

LLB

14

RLB

15

TAOS

2

TxLEV

1

ENCODIS

21

REQDIS

12

T1

1:1

1

5

4

8

T2

1:1

1

5

4

8

R1

36

1

2

R2

36

1

2

R6

37.5

1

2

R3

270

1

2

R4

270

1

2

R5

37.5

1

2

C1

0.01uF

1

2

TxSER

TxInClk

NIBBLEINTF

RESETB

RTIP

RRING

CSB

RW

DS

AS

TxFrame

RxSer

RxClk

RxFrame

RxLOS

RxOOF

RxRED

RxAIS

A[8:0]

TRING

TTIP

INTB

D[7:0]

INTB

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| XRT72L53IB-F | IC FRAMER DS3/E3 3CH 272PBGA |

| XRT72L54IB | IC FRAMER DS3/E3 4CH 272PBGA |

| XRT72L71IQ | IC FRAMER DS3 ATM UNI 160PQFP |

| XRT73L02MIV-F | IC LIU E3/DS3/STS-1 2CH 100TQFP |

| XRT73L03BIV-F | IC LIU E3/DS3/STS-1 3CH 120LQFP |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| XRT72L53 | 鍒堕€犲晢:EXAR 鍒堕€犲晢鍏ㄧū:EXAR 鍔熻兘鎻忚堪:THREE CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER |

| XRT72L53-75L03DPC | 鍔熻兘鎻忚堪:缍�(w菐ng)绲�(lu貌)鎺у埗鍣ㄨ垏铏曠悊鍣� IC with T75L03D. RoHS:鍚� 鍒堕€犲晢:Micrel 鐢�(ch菐n)鍝�:Controller Area Network (CAN) 鏀剁櫦(f膩)鍣ㄦ暩(sh霉)閲�: 鏁�(sh霉)鎿�(j霉)閫熺巼: 闆绘簮闆绘祦锛堟渶澶у€硷級:595 mA 鏈€澶у伐浣滄韩搴�:+ 85 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:PBGA-400 灏佽:Tray |

| XRT72L53-75L03PCI | 鍔熻兘鎻忚堪:缍�(w菐ng)绲�(lu貌)鎺у埗鍣ㄨ垏铏曠悊鍣� IC with T75L03. RoHS:鍚� 鍒堕€犲晢:Micrel 鐢�(ch菐n)鍝�:Controller Area Network (CAN) 鏀剁櫦(f膩)鍣ㄦ暩(sh霉)閲�: 鏁�(sh霉)鎿�(j霉)閫熺巼: 闆绘簮闆绘祦锛堟渶澶у€硷級:595 mA 鏈€澶у伐浣滄韩搴�:+ 85 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:PBGA-400 灏佽:Tray |

| XRT72L53ES-75L03D-PCI | 鍔熻兘鎻忚堪:鐣岄潰闁嬬櫦(f膩)宸ュ叿 Evaluation Board for XRT72L53 Series RoHS:鍚� 鍒堕€犲晢:Bourns 鐢�(ch菐n)鍝�:Evaluation Boards 椤炲瀷:RS-485 宸ュ叿鐢ㄤ簬瑭曚及:ADM3485E 鎺ュ彛椤炲瀷:RS-485 宸ヤ綔闆绘簮闆诲:3.3 V |

| XRT72L53ES-PCI | 鍔熻兘鎻忚堪:缍�(w菐ng)绲�(lu貌)鎺у埗鍣ㄨ垏铏曠悊鍣� IC withT73LC03A+T71D03 RoHS:鍚� 鍒堕€犲晢:Micrel 鐢�(ch菐n)鍝�:Controller Area Network (CAN) 鏀剁櫦(f膩)鍣ㄦ暩(sh霉)閲�: 鏁�(sh霉)鎿�(j霉)閫熺巼: 闆绘簮闆绘祦锛堟渶澶у€硷級:595 mA 鏈€澶у伐浣滄韩搴�:+ 85 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:PBGA-400 灏佽:Tray |

鐧�(f膩)甯冪穵鎬ラ噰璩硷紝3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�