- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄372949 > XRT7302IV PCM Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | XRT7302IV |

| 英文描述: | PCM Transceiver |

| 中文描述: | 收發(fā)器的PCM |

| 文件頁(yè)數(shù): | 10/53頁(yè) |

| 文件大小: | 604K |

| 代理商: | XRT7302IV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

XRT73L00

E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.2.0

á

7

22

CS/(DR/SR)

I

Microprocessor Serial Interface - Chip Select/Encoder and Decoder Dis-

able

The function of this input pin depends upon whether the XRT73L00 is operating

in the HOST or the Hardware Mode.

HOST Mode - Chip Select Input:

The Local Microprocessor must assert this pin (e.g., set it to “0”) in order to

enable communication with the XRT73L00 via the Microprocessor Serial Inter-

face.

Hardware Mode - Dual-Rail/Single-Rail Select Input:

Setting this input pin “High” configures the XRT73L00 to operate in the Dual-Rail

Mode. When the XRT73L00 is operating in this mode, then the Receive Section

of the LIU IC outputs the Recovered Data via both RPOS and RNEG output pins.

Setting this input pin “Low” configures the XRT73L00 to operate in the Single-

Rail Mode. When the XRT73L00 is operating in this mode, the Receive Section

of the LIU IC outputs the Recovered Data via the RPOS output pin in a binary

data stream. No data will output via the RNEG output pin.

23

RLOL

O

Receive Loss of Lock Output Indicator

This output pin toggles “High” if the XRT73L00 has detected a Loss of Lock Con-

dition. The XRT73L00 declares an LOL (Loss of Lock) Condition if the recovered

clock frequency deviates from the Reference Clock frequency (available at the

EXCLK input pin) by more than 0.5%.

N

OTE

:

The RCLK1/2 output pins are sourced by the signal applied at the EXCLK

input pin anytime the XRT73L00 declares an LOL condition.

24

RLOS

O

Receive Loss of Signal Output Indicator

This output pin toggles “High” if the XRT73L00 has detected a Loss of Signal

Condition in the incoming line signal.

The criteria the XRT73L00 uses to declare an LOS Condition depends upon

whether the device is operating in the E3 or DS3/STS-1 Mode.

25

DGND

****

Digital Ground

26

DVDD

****

Digital Power Supply

27

EXCLK

I

External Reference Clock Input:

Apply a line-rate clock signal to this input pin. This signal is a 34.368MHz clock

signal for E3 applications, a 44.736 MHz clock signal for DS3 applications or a

51.84 MHz clock signal for SONET STS-1 applications.

N

OTE

:

This input pin functions as the source of the RxCLK output clock signal

any time the XRT73L00 declares an LOL condition.

28

RxDGND

****

Receiver Digital Ground

29

RxDVDD

****

Receiver Digital Power Supply

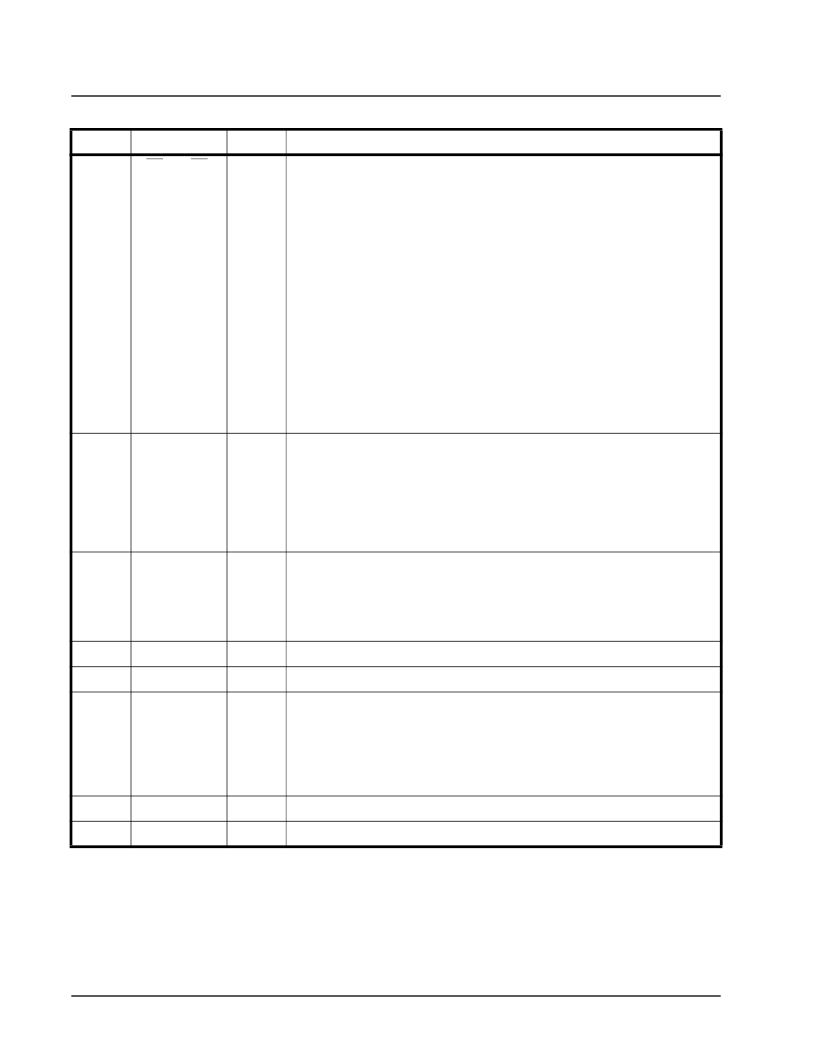

PIN DESCRIPTION

P

IN

#

S

YMBOL

T

YPE

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT73L03 | 3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT |

| XRT73L03IV | 3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT |

| XRT73LC00 | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73LC00IV | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00 | E3/DS3/STS-1 LINE INTERFACE UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT73L00 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00A | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00AES | 功能描述:界面開(kāi)發(fā)工具 Eval System for XRT73L00A Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XRT73L00AIV | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00IV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LINE INTERFACE|QFP|44PIN|PLASTIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。