- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT73L04AIV (EXAR CORP) 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT PDF資料下載

參數(shù)資料

| 型號(hào): | XRT73L04AIV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, HEAT SINK, TQFP-144 |

| 文件頁數(shù): | 10/65頁 |

| 文件大小: | 366K |

| 代理商: | XRT73L04AIV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

XRT73L04A

4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT

REV. 2.0.3

6

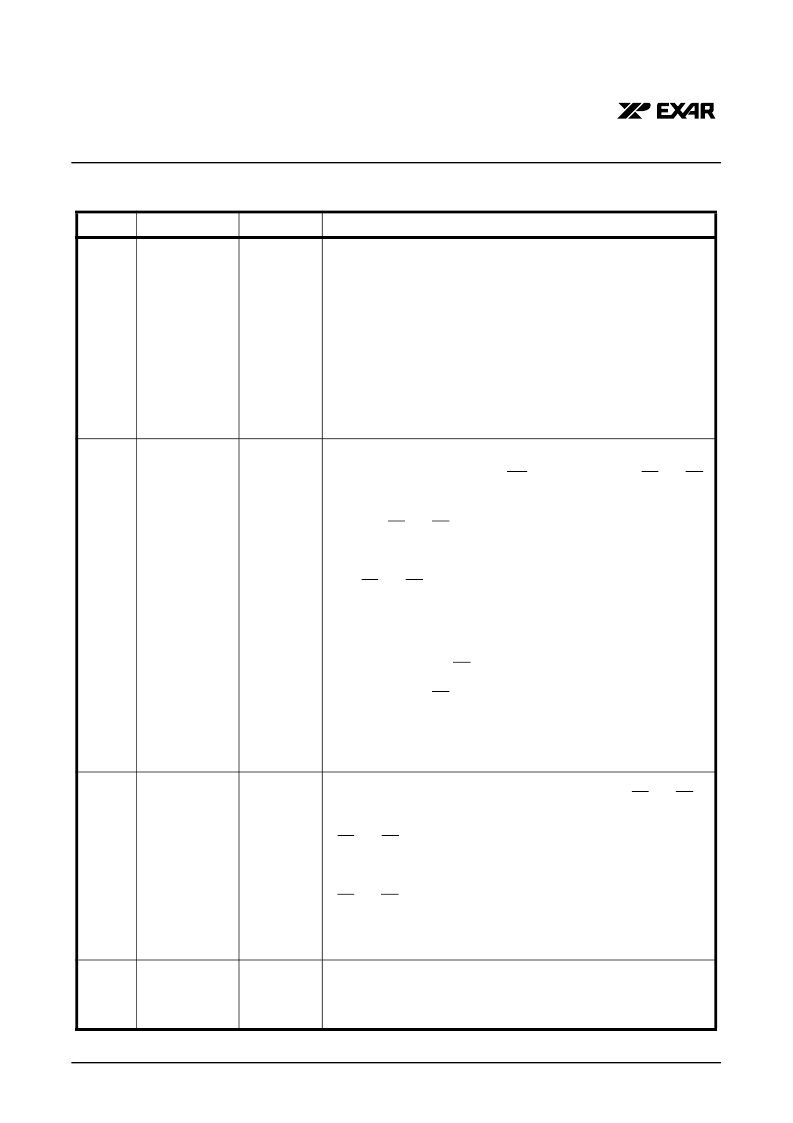

RECEIVE INTERFACE

P

IN

#

N

AME

T

YPE

D

ESCRIPTION

59

53

121

127

RxClk_0

RxClk_1

RxClk_2

RxClk_3

O

R

eceive Clock Output - Channel (n):

This output pin is the Recovered Clock signal from the incoming line sig-

nal for Channel (n). The Receive Section of Channel (n) outputs data via

the RPOS_(n) and RNEG_(n) output pins on the rising edge of this clock

signal.

Configure the Receive Section of Channel (n) to update the data on the

RPOS_(n) and RNEG_(n) output pins on the falling edge of RxClk_(n)

by doing one of the following:

a.

Operating in the Hardware Mode

Pull the RxClkINV pin to "High".

b.

Operating in the HOST Mode

Write a "1" into the RxClkINV bit-field within the Command Register.

60

54

120

126

RNEG_0/LCV_0

RNEG_1/LCV_1

RNEG_2/LCV_2

RNEG_3/LCV_3

O

Receive Negative Data Output - Channel (n):

The function of this pin is dependent on whether the 73L04A is in the

Hardware or HOST Mode (HOST/HW) and the condition of CS/(SR/DR).

a.

Operating in the Hardware Mode

Receive Negative Data:

Setting the CS/(SR/DR

) pin ”Low”, (Dual-Rail operation) this output pin

pulses "High" whenever Channel (n) has received a Negative Polarity

pulse in the incoming line signal at the RTIP_(n) and RRing_(n) inputs.

Line Code Violation:

When CS/(SR/DR) is set “High”, (Single-Rail operation), the B3ZS/HDB3

Encoder/Decoder is activated and the Line Code Violation signal is out-

put on this pin.

b.

Operating in the HOST Mode

Receive Negative Data:

Writing a “0” to the (SR/DR)_(n) bit in the command register configures

channel(n) in the Dual-Rail Mode and activates RNEG_(n).

Writing a “1” to (SR/DR)_(n) bit of the Command Register configures the

Single-Rail Mode and activates LCV_(n).

If the B3ZS/HDB3 Decoder is enabled then the zero suppression pat-

terns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V")

is not reflected at this output.

61

55

119

125

RPOS_0

RPOS_1

RPOS_2

RPOS_3

O

Receive Positive Data Output - Channel (n):

The function of this pin is dependent on the setting of the CS/(SR/DR)

pin.

Receive Positive Data

If CS/(SR/DR) is set “Low” (Dual-Rail Mode), this output pin pulses

"High" whenever Channel (n) has received a Positive Polarity pulse in

the incoming line signal at the RTIP_(n)/RRing_(n) inputs.

Data Output

If CS/(SR/DR) is set “High” (Single-Rail Mode), data is output on this pin.

If the B3ZS/HDB3 Decoder is enabled then the zero suppression pat-

terns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V")

is not reflected at this output.

79

87

102

94

RRing_0

RRing_1

RRing_2

RRing_3

I

Receive Ring Input - Channel (n):

This input pin along with RTIP_(n) is used to receive the bipolar line sig-

nal from the Remote DS3/E3/STS-1 Terminal.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT73L04B | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04BIV | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04 | 4 Channel E3/DS3/STS-1 Line Interface Unit(4通道 E3/DS3/STS-1線接口單元) |

| XRT73L06 | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L06IB | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT73L04B | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04BES | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT73L04BIV | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT73L04BIV-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT73L06 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。