- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT8000ID (EXAR CORP) Clock Synchronizer/Adapter for Communications PDF資料下載

參數(shù)資料

| 型號: | XRT8000ID |

| 廠商: | EXAR CORP |

| 元件分類: | XO, clock |

| 英文描述: | Clock Synchronizer/Adapter for Communications |

| 中文描述: | 2.048 MHz, OTHER CLOCK GENERATOR, PDSO18 |

| 封裝: | 0.300 INCH, SOIC-18 |

| 文件頁數(shù): | 3/24頁 |

| 文件大小: | 513K |

| 代理商: | XRT8000ID |

XRT8000

3

Rev. 1.11

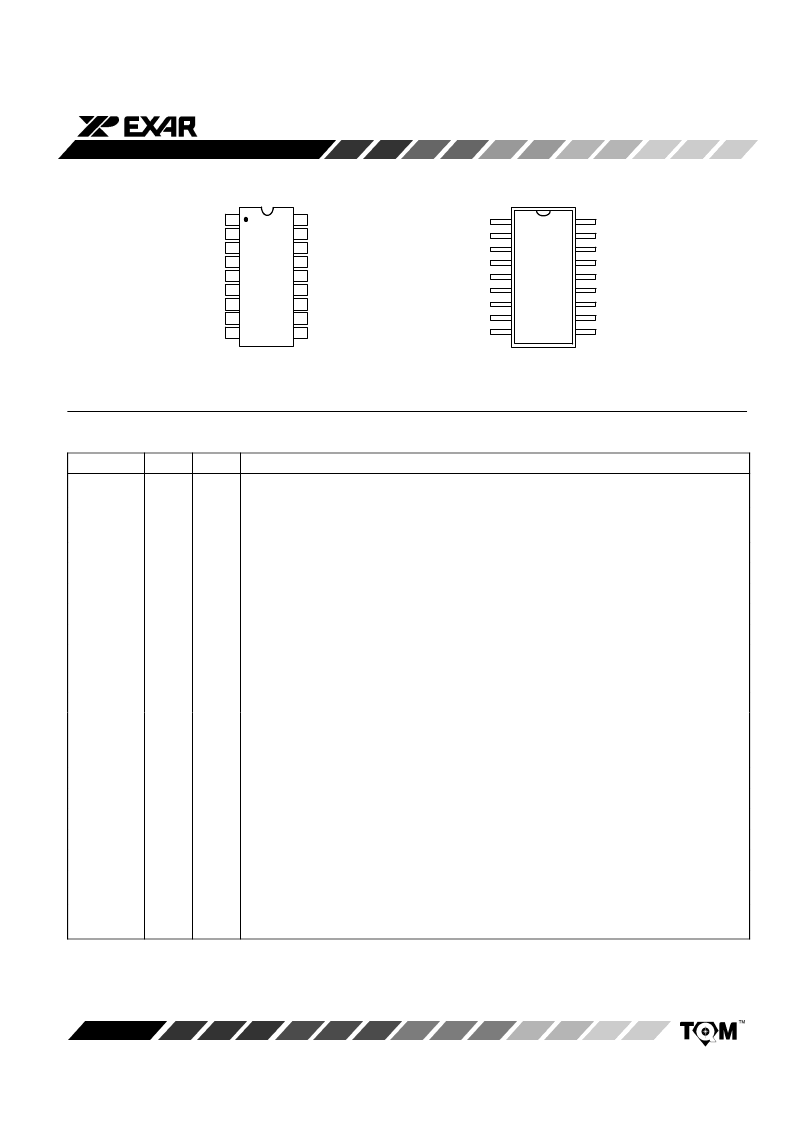

PIN CONFIGURATION

SCLK

CSB

SDI

V

CC

GND

CLK2

V

CC

LOCKDET

V

CC

SDO

SYNC

F

IN

GND

GND

CLK1

V

CC

MSB

GND

18 Lead PDIP (0.300”)

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

18 Lead SOIC (Jedec, 0.300”)

SCLK

CSB

SDI

V

CC

GND

CLK2

V

CC

LOCKDET

V

CC

SDO

SYNC

F

IN

GND

GND

CLK1

V

CC

MSB

GND

18

1

10

9

2

3

4

5

6

7

8

15

14

13

12

11

17

16

PIN DESCRIPTION

Symbol

SDO

Pin#

1

Type

O

Description

Serial Data Output (Microprocessor Serial Interface).

Data output from the command reg-

isters.

SYNC

2

O

An 8kHz Signal SubDivided From F

IN.

This output can be threestated via CR5. SYNC can

be used to synchronize other XRT8000 which are configured in slave modes.

F

IN

GND

GND

CLK1

V

CC

MSB

3

4

5

6

7

I

Reference Frequency Input.

Digital Ground.

Digital Ground.

Clock 1.

Output of the phase-locked loop 1.

Digital Positive Power Supply.

O

8

I

Master/Slave Mode Select Input.

If this input is high, then the MASTER mode is selected. If

this input is low, then the SLAVE mode is enabled. This pin is internally pulled up via 100K

resistor.

GND

V

CC

9

Analog Ground.

Analog Positive Supply.

10

LOCKDET

11

O

Lock Detect.

This output is high when both phase-locked loops are in lock and will go low if

either one of the phase locked loops loses lock.

V

CC

CLK2

GND

V

CC

SDI

CSB

12

13

14

15

16

17

Digital Positive Power Supply.

Clock 2.

Output of the phase-locked loop 2.

Digital Ground.

Digital Positive Power Supply.

Serial Data Input (Microprocessor Serial Interface)

Data input to the command registers.

Chip Select Not (Microprocessor Serial Interface) .

When this input is low the data in and

out will be shifted in the appropriate registers. Internal pull up (100K).

O

I

I

SCLK

18

I

Serial Clock Input (Microprocessor Serial Interface) .

This clock will serve as a reference

to the data streams to SDI and SDO (the positive edge of SCLK is used to latch the data).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT8000 | Clock Synchronizer/Adapter for Communications(用于通訊的時(shí)鐘同步設(shè)備/調(diào)整器) |

| XRT8001 | WAN Clock for T1 and E1 Systems |

| XRT8001ID | WAN Clock for T1 and E1 Systems |

| XRT8001IP | WAN Clock for T1 and E1 Systems |

| XRT8010 | 312MHZ CLOCK & CRYSTAL MULTIPLIER WITH LVDS OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR-T8000ID | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Miscellaneous Clock Generator |

| XRT8000ID-F | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 3.3V-5V 0.05UI temp -45 to 85C RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT8000IDTR-F | 功能描述:鎖相環(huán) - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| XRT8000IP | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

| XRT8000IP-F | 功能描述:鎖相環(huán) - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。