- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9689 > XRT91L32IQ (Exar Corporation)IC TXRX SONET/SDH 8BIT 100QFP PDF資料下載

參數(shù)資料

| 型號: | XRT91L32IQ |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 16/37頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC TXRX SONET/SDH 8BIT 100QFP |

| 產(chǎn)品變化通告: | XRT91L32IQ(TR) Obsolescence 12/Oct/2010 |

| 標準包裝: | 90 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | SONET/SDH |

| 電源電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-BQFP |

| 供應商設備封裝: | 100-QFP(14x20) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

xr

XRT91L32

REV. 1.0.3

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

21

3.0

TRANSMIT SECTION

The transmit section of the XRT91L32 accepts 8-bit parallel data and converts it to serial Differential LVPECL

data output intented to interface to an optical module. It consists of an 8-bit parallel Single-Ended LVTTL

interface, Parallel-to-Serial Converter, a clock multiplier unit (CMU), a Low Voltage Positive-referenced Emitter-

Coupled Logic (LVPECL) differential line driver, and Loop Timing modes. The LVPECL serial data output rate is

622.08 Mbps for STS-12/STM-4 applications and 155.52 Mbps for STS-3/STM-1 applications. The high

frequency serial clock is synthesized by a PLL, which uses a low frequency clock as its input reference. In

order to synchronize the data transfer process, the synthesized 622.08 MHz for STS-12/STM-4 or 155.52 MHz

STS-3/STM-1 serial clock output is divided by eight and the 77.76 MHz (STS-12/STM-4) or 19.44 MHz (STS-3/

STM-1) clock respectively is presented to the framer/mapper device to be used as its timing source.

3.1

Transmit Parallel Input Interface

The parallel data from an framer/mapper device is presented to the XRT91L32 through an 8-bit Single-Ended

LVTTL parallel bus interface TXDI[7:0]. To directly interface to the XRT91L32, the SONET Framer/ASIC must

be synchronized to the same timing source TXPCLK_IO in presenting data on the parallel bus interface. The

data must meet setup and hold times with respect to TXPCLK_IO. This clock output source is used to

synchronize the SONET Framer/ASIC to the XRT91L32. The framer/mapper device should use TXPCLK_IO

as its timing source so that parallel data is phase aligned with the serial transmit data. The data is latched into

a parallel input register on the rising edge of TXPCLK_IO. TXPCLK_IO is derived from a divide-by-8 of the high

speed synthesized clock resulting in a 77.76/ 19.44 MHz Single-Ended LVTTL clock output source to be used

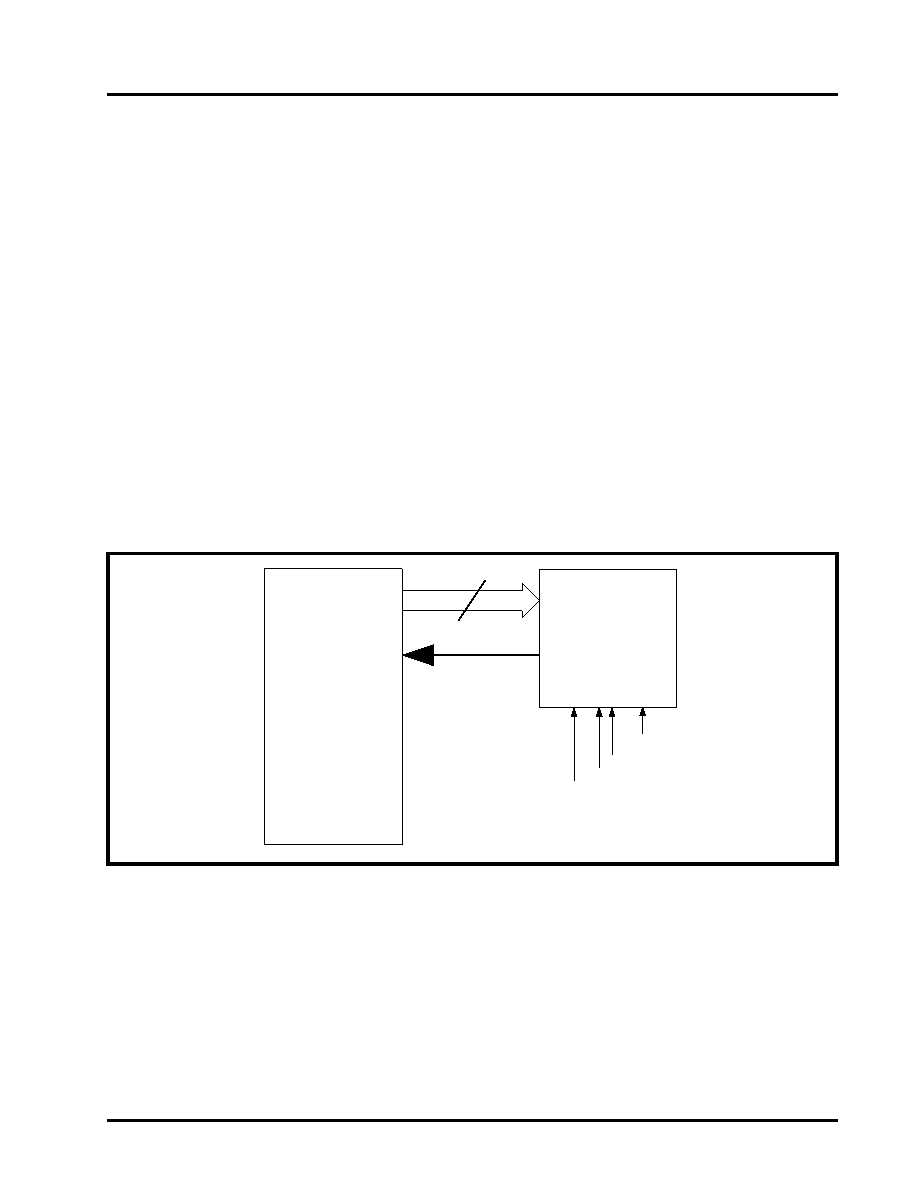

by the framer/mapper device for parallel bus synchronization. A simplified block diagram of the transmit

parallel bus clock output system interface is shown in Figure 11.

FIGURE 11. TRANSMIT PARALLEL INPUT INTERFACE BLOCK

SONET Framer/ASIC

REFCLKP

TXPCLK_IO

TTLREFCLK

TXDI[7:0]

8

CMUREFSEL

REFCLKN

XRT91L32

STS-12/STM-4

or

STS-3/STM-1

Transceiver

相關PDF資料 |

PDF描述 |

|---|---|

| M83723/78R1002N | CONN PLUG 2POS STRAIGHT W/PINS |

| VE-JTL-MX-F3 | CONVERTER MOD DC/DC 28V 75W |

| M83723/83A1006N | CONN RCPT 6POS WALL MT W/PINS |

| VE-JTL-MX-F1 | CONVERTER MOD DC/DC 28V 75W |

| MS27508E20B41PD | CONN RCPT 41POS BOX MNT W/PINS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L32IQ-F | 功能描述:總線收發(fā)器 8-Bit TTL 3.3V temp -45 to 85C;UART RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L32IQTR | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQTR-F | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L33 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

| XRT91L33AIG-F | 制造商:Exar Corporation 功能描述:CDR 155.52Mbps/622.08Mbps SONET/SDH 20-Pin TSSOP |

發(fā)布緊急采購,3分鐘左右您將得到回復。