- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30120GGG2 (ZARLINK SEMICONDUCTOR INC) SONET/SDH/Ethernet Multi-Rate Line Card Synchronizer PDF資料下載

參數(shù)資料

| 型號(hào): | ZL30120GGG2 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | SONET/SDH/Ethernet Multi-Rate Line Card Synchronizer |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA100 |

| 封裝: | 9 X 9 MM, 0.80 MM PITCH, LEAD FREE, CABGA-100 |

| 文件頁(yè)數(shù): | 1/27頁(yè) |

| 文件大?。?/td> | 309K |

| 代理商: | ZL30120GGG2 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2006, Zarlink Semiconductor Inc. All Rights Reserved.

A full Design Manual is available to qualified customers.

To

register,

please

TimingandSync@Zarlink.com.

send

an

email

to

Features

Synchronizes with standard telecom system

references and synthesizes a wide variety of

protected telecom line interface clocks that are

compliant with Telcordia GR-1244-CORE, GR-253-

CORE, ITU-T G.813, and compatible with ITU-T

G.8261 (formerly G.pactiming)

Internal low jitter APLL provides SONET/SDH

clocks including 6.48 MHz, 19.44 MHz, 38.88 MHz,

51.84 MHz and 77.76 MHz, or 25 MHz and 50 MHz

Synchronous Ethernet output clocks

Programmable output synthesizers (P0, P1)

generate general purpose clock frequencies from

any multiple of 8 kHz up to 100 MHz

Jitter performance of <8 ps RMS on the low jitter

APLL outputs, and <20 ps RMS on the

programmable synthesizer outputs.

Provides 8 reference inputs which support clock

frequencies with any multiples of 8 kHz up to

77.76 MHz in addition to 2 kHz

Provides two DPLLs which have independent

modes of operation (locked, free-run, holdover)

and optional hitless reference switching.

Flexible input reference monitoring automatically

disqualifies references based on frequency and

phase irregularities

Provides 3 sync inputs for output frame pulse

alignment

Generates several styles of output frame pulses

with selectable pulse width, polarity, and frequency

Configurable input to output delay, and output to

output phase alignment

Supports IEEE 1149.1 JTAG Boundary Scan

May 2006

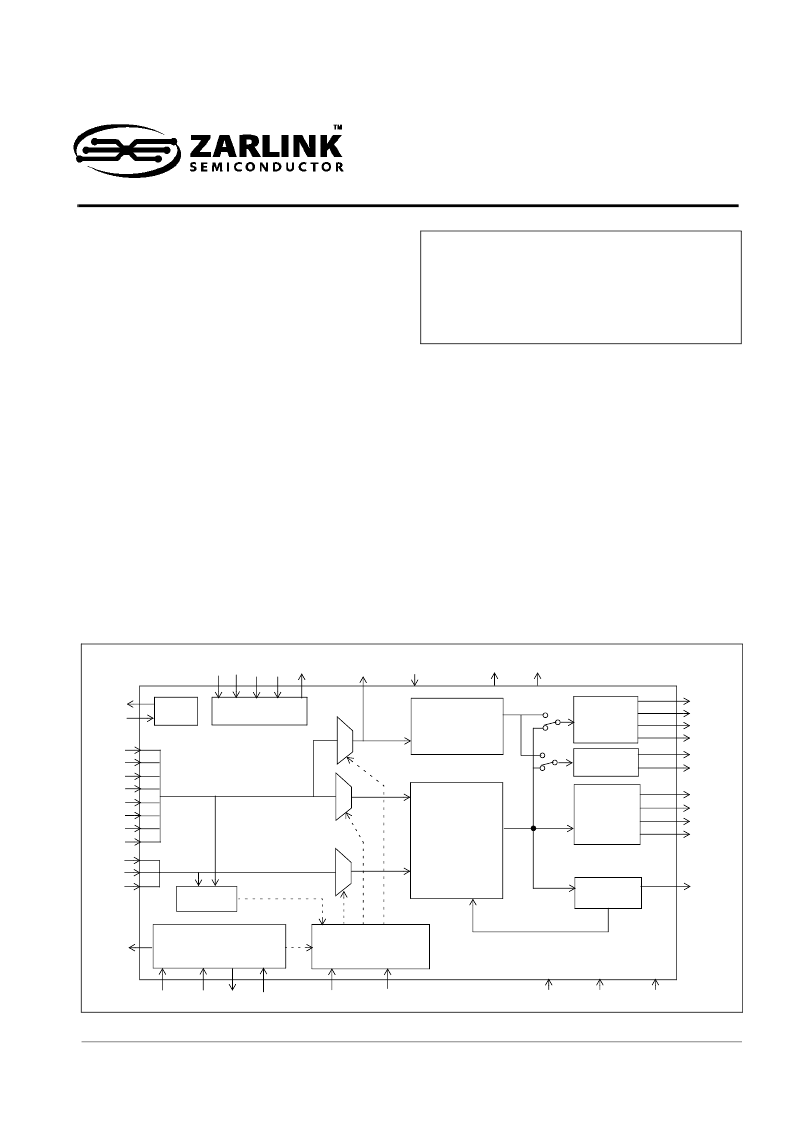

Figure 1 - Block Diagram

dpll1_mod_sel1:0

tck

tdo

tdi tms

trst_b

dpll1_holdover

dpll1_lock

DPLL2

sck

so

si

DPLL1

dpll2_ref

rst_b

dpll1_hs_en

cs_b

Reference

Monitors

ref

sync

ref

ref0

ref1

ref2

ref3

ref4

ref5

ref6

ref7

sync0

sync1

sync2

int_b

apll_clk0

apll_clk1

apll_fp0

apll_fp1

p0_clk0

p0_clk1

p0_fp0

p0_fp1

p1_clk0

p1_clk1

fb_clk

ref7:0

sync2:0

ref_&_sync_status

Controller &

State Machine

SPI Interface

Low Jitter

APLL

P0

Synthesizer

P1

Synthesizer

Feedback

Synthesizer

IEEE 1449.1

JTAG

Master

Clock

osco

osci

fb_clk/fp

apll_filter

filter_ref0

filter_ref1

ZL30120

SONET/SDH/Ethernet

Multi-Rate Line Card Synchronizer

Data Sheet

Ordering Information

ZL30120GGG

ZL30120GGG2

100 Pin CABGA

100 Pin CABGA**

**Pb Free Tin/Silver/Copper

Trays

Trays

-40

o

C to +85

o

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30121GGG2 | SONET/SDH Low Jitter System Synchronizer |

| ZL30121 | SONET/SDH Low Jitter System Synchronizer |

| ZL30121GGG | SONET/SDH Low Jitter System Synchronizer |

| ZL30122 | SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30122GGG | SONET/SDH Low Jitter Line Card Synchronizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30121 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Low Jitter System Synchronizer |

| ZL30121GGG | 制造商:Microsemi Corporation 功能描述:SYS SYNCHRONIZER 100CABGA - Trays |

| ZL30121GGG2 | 制造商:Microsemi Corporation 功能描述:PB FREE LOW JITTER SYSTEM SYNCHRONIZER |

| ZL30121GGG2V2 | 制造商:Microsemi Corporation 功能描述:REV 2 PB FREE LOW JITTER SYSTEM SYNCHRO 制造商:Microsemi Corporation 功能描述:REV 2 PB FREE LOW JITTER SYSTEM SYNCHRO - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SONET/SDH SYNCH 100CABGA 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 100CABGA |

| ZL30121GGGV2 | 制造商:Microsemi Corporation 功能描述:LOW JITTER SYSTEM SYNCHRONIZER 制造商:Microsemi Corporation 功能描述:REV 2 LOW JITTER SYSTEM SYNCHRONIZER - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SONET/SDH SYNCH 100CABGA 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 100CABGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。