- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300164 > ZL30402/QCG1 (ZARLINK SEMICONDUCTOR INC) ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | ZL30402/QCG1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026BEC, LQFP-80 |

| 文件頁(yè)數(shù): | 18/44頁(yè) |

| 文件大小: | 472K |

| 代理商: | ZL30402/QCG1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

ZL30402

Data Sheet

25

Zarlink Semiconductor Inc.

Address: 14 H

Address: 19 H

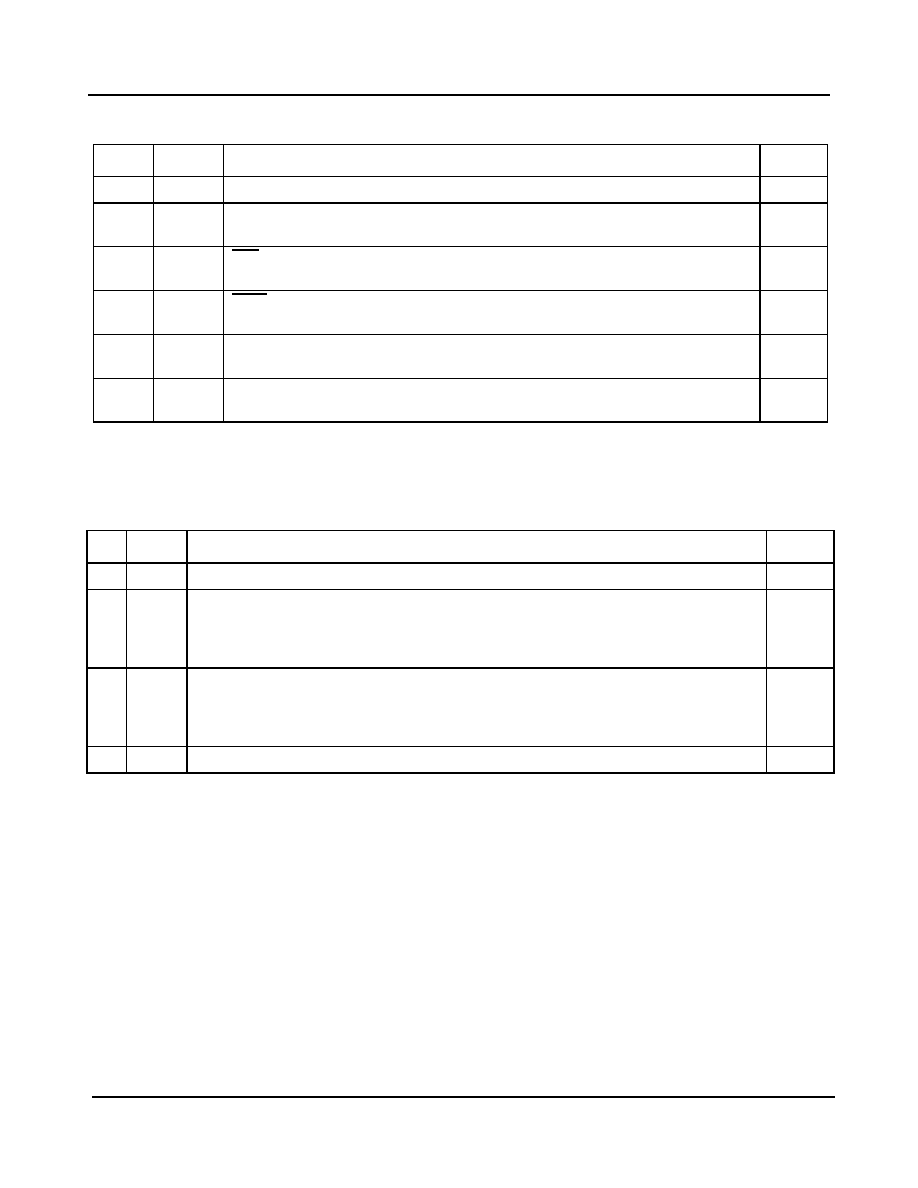

Bit

Name

Functional Description

Default

7-5

RSV

Reserved.

000

4

F8odis

F8o Frame Pulse Disable. When set high, this bit tristates the 8 kHz 122 ns

active high framing pulse output.

0

3

F0odis

F0o Frame Pulse Disable. When set high, this bit tristates the 8 kHz 244 ns

active low framing pulse output.

0

2

F16odis

F16o Frame Pulse Disable. When set high, this bit tristates the 8 kHz 61 ns

active low framing pulse output.

0

1C6dis

6.312 MHz Clock Disable. When set high, this bit tristates the 6.312 MHz clock

output.

0

C19dis

19.44 MHz Clock Disable. When set high, this bit tristates the 19.44 MHz clock

output.

0

Table 13 - Clock Disable Register 2 (R/W)

Bit

Name

Functional Description

Default

7-3

RSV

Reserved.

00000

2MHR

Manual Holdover Release. A change form 0 to 1 on the MHR bit will release the Core

PLL from Auto Holdover to Normal when automatic return from Holdover is disabled

(AHRD is set to 1). This bit is level sensitive and it must be cleared immediately after it

is set to 1 (next write operation). This bit has no effect if AHRD is set to 0.

0

1

AHRD

Automatic Holdover Return Disable. When set high, this bit inhibits the Core PLL

from automatically switching back to Normal mode from Auto Holdover state when the

active Acquisition PLL regains lock to input reference. The active Acquisition PLL is the

Acquisition PLL to which the Core PLL is currently connected.

0

0RSV

Reserved.

0

Table 14 - Core PLL Control Register (R/W)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50112GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30406 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | 制造商:Zarlink Semiconductor Inc 功能描述:PLL CLOCK MLTPLR SGL UP TO 19.44MHZ 64TQFP - Trays |

| ZL30406QGC1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGG1 | 制造商:Microsemi Corporation 功能描述:IC PB FREE T1/E1 SYS. SYNC+STRATUM 3 H/O 制造商:Microsemi Corporation 功能描述:PB FREE SONET/SDH CLOCK MULTIPLIER PLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP 制造商:Microsemi Corporation 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。