- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1887 > 100-1221-3 (Bluetechnix)CORE MOD CM-BF537E 600MHZ CONN PDF資料下載

參數(shù)資料

| 型號(hào): | 100-1221-3 |

| 廠商: | Bluetechnix |

| 文件頁(yè)數(shù): | 6/68頁(yè) |

| 文件大小: | 0K |

| 描述: | CORE MOD CM-BF537E 600MHZ CONN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 模塊/板類型: | 核心模塊 |

| 其它名稱: | 100-1221 100-1221-ND |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

Rev. J

|

Page 14 of 68

|

February 2014

Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling

the voltage and clocks to the processor core (CCLK) and to all of

the synchronous peripherals (SCLK). The internal voltage regu-

lator for the processor can be shut off by writing b#00 to the

FREQ bits of the VR_CTL register. This disables both CCLK

and SCLK. Furthermore, it sets the internal power supply volt-

age (VDDINT) to 0 V to provide the greatest power savings. To

preserve the processor state, prior to removing power, any criti-

cal information stored internally (memory contents, register

contents, etc.) must be written to a nonvolatile storage device.

Since VDDEXT is still supplied in this state, all of the external pins

three-state, unless otherwise specified. This allows other devices

that are connected to the processor to still have power applied

without drawing unwanted current.

The Ethernet or CAN modules can wake up the internal supply

regulator. If the PH6 pin does not connect as the PHYINT sig-

nal to an external PHY device, it can be pulled low by any other

device to wake the processor up. The regulator can also be

woken up by a real-time clock wake-up event or by asserting the

RESET pin. All hibernate wake-up events initiate the hardware

reset sequence. Individual sources are enabled by the VR_CTL

register.

With the exception of the VR_CTL and the RTC registers, all

internal registers and memories lose their content in the hiber-

nate state. State variables can be held in external SRAM or

SDRAM. The SCKELOW bit in the VR_CTL register provides a

means of waking from hibernate state without disrupting a self-

refreshing SDRAM, provided that there is also an external pull-

down on the SCKE pin.

Power Savings

As shown in Table 5, the processors support three different

power domains which maximizes flexibility, while maintaining

compliance with industry standards and conventions. By isolat-

ing the internal logic of the processor into its own power

domain, separate from the RTC and other I/O, the processor

can take advantage of dynamic power management, without

affecting the RTC or other I/O devices. There are no sequencing

requirements for the various power domains.

The dynamic power management feature allows both the pro-

cessor’s input voltage (VDDINT) and clock frequency (fCCLK) to be

dynamically controlled.

The power dissipated by a processor is largely a function of its

clock frequency and the square of the operating voltage. For

example, reducing the clock frequency by 25% results in a 25%

reduction in power dissipation, while reducing the voltage by

25% reduces power dissipation by more than 40%. Further,

these power savings are additive, in that if the clock frequency

and supply voltage are both reduced, the power savings can be

dramatic, as shown in the following equations.

The power savings factor (PSF) is calculated as:

where:

fCCLKNOM is the nominal core clock frequency

fCCLKRED is the reduced core clock frequency

VDDINTNOM is the nominal internal supply voltage

VDDINTRED is the reduced internal supply voltage

tNOM is the duration running at fCCLKNOM

tRED is the duration running at fCCLKRED

The percent power savings is calculated as

VOLTAGE REGULATION

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors pro-

vide an on-chip voltage regulator that can generate appropriate

Conditions on Page 23 for regulator tolerances and acceptable

VDDEXT ranges for specific models.

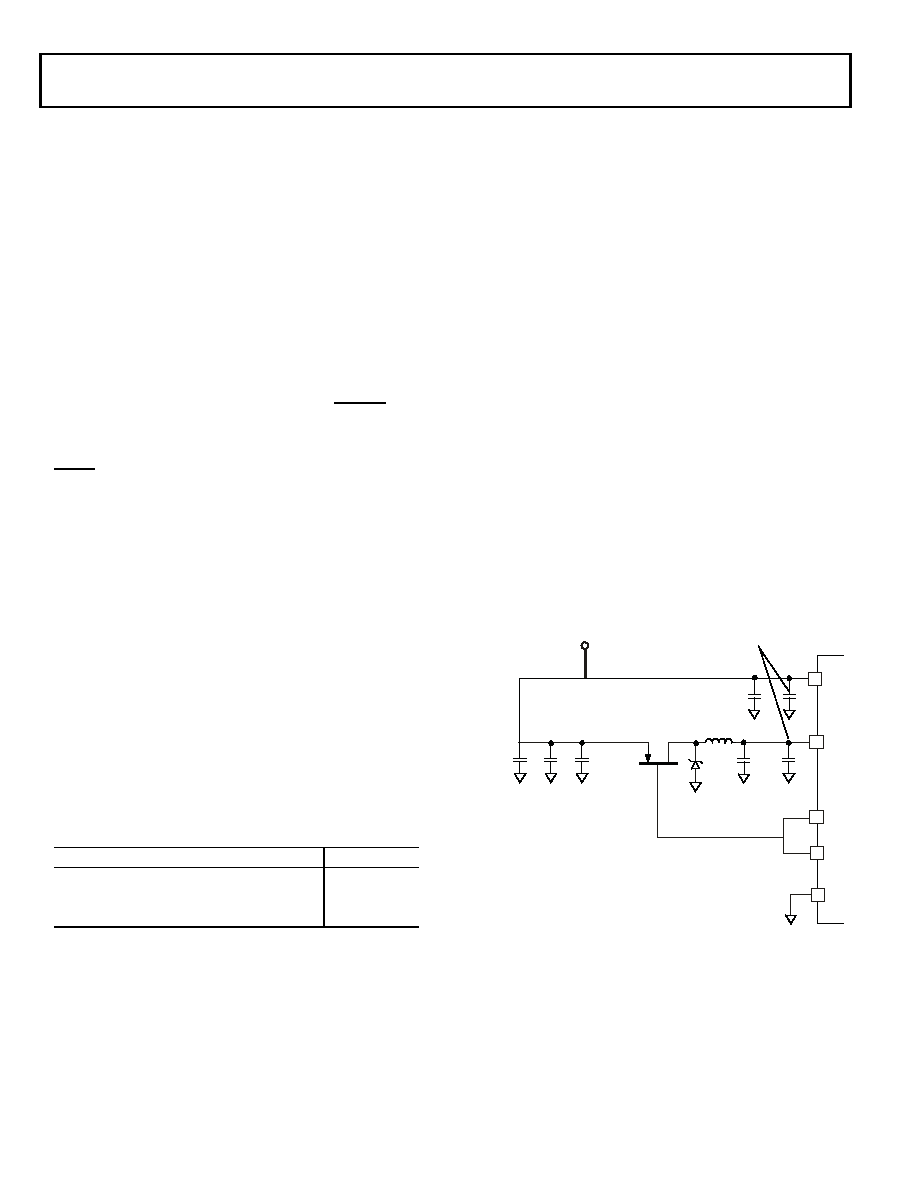

Figure 5 shows the typical external components required to

complete the power management system. The regulator con-

trols the internal logic voltage levels and is programmable with

the voltage regulator control register (VR_CTL) in increments

of 50 mV. To reduce standby power consumption, the internal

voltage regulator can be programmed to remove power to the

processor core while keeping I/O power supplied. While in

Table 5. Power Domains

Power Domain

VDD Range

All internal logic, except RTC

VDDINT

RTC internal logic and crystal I/O

VDDRTC

All other I/O

VDDEXT

Figure 5. Voltage Regulator Circuit

PSF

fCCLKRED

fCCLKNOM

---------------------

VDDINTRED

VDDINTNOM

--------------------------

2

tRED

-----------

=

% power savings

1

PSF

–

100%

=

VDDEXT

(LOW-INDUCTANCE)

VDDINT

VROUT

100μF

VROUT

GND

SHORT AND LOW-

INDUCTANCE WIRE

VDDEXT

+

100μF

10μF

LOW ESR

100nF

SET OF DECOUPLING

CAPACITORS

FDS9431A

ZHCS1000

NOTE: DESIGNER SHOULD MINIMIZE

TRACE LENGTH TO FDS9431A.

10μH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 100-1225-1 | CORE MOD TCM-BF537 500MHZ CONN |

| 100-1254-2 | MODULE BF527-C-C-Q50S64F8 |

| 101-0303 | SMARTSCREEN OP7100 DISPLAY |

| 101-0383 | MODULE RABBITCORE RCM2020 |

| 101-0435 | MODULE RABBITCORE RCM2110 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 1001224 | 功能描述:防靜電控制產(chǎn)品 12X24 PKG/100 RoHS:否 制造商:3M Electronic Specialty 產(chǎn)品:Air Ionizers 類型:Mini 顏色: 大小:4.5 in x 3.3 in x 2 in |

| 1001225 | 功能描述:防靜電控制產(chǎn)品 12X25 PKG/100 RoHS:否 制造商:3M Electronic Specialty 產(chǎn)品:Air Ionizers 類型:Mini 顏色: 大小:4.5 in x 3.3 in x 2 in |

| 100-1225-1 | 功能描述:CORE MOD TCM-BF537 500MHZ CONN RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微控制器或微處理器模塊 系列:- 產(chǎn)品目錄繪圖:DLP-245SY-G 標(biāo)準(zhǔn)包裝:1 系列:USB 模塊/板類型:開(kāi)發(fā)板 適用于相關(guān)產(chǎn)品:USB 其它名稱:813-1006 |

| 10-01-2259 | 功能描述:集管和線殼 KK 100 Housing Crimp Crimp Std 25 Ckt RoHS:否 產(chǎn)品種類:1.0MM Rectangular Connectors 產(chǎn)品類型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| 100122A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Nine Bit Buffer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。