- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370035 > 28222-14 (Conexant Systems, Inc.) ATM Transmitter/Receiver with UTOPIA Interface PDF資料下載

參數(shù)資料

| 型號(hào): | 28222-14 |

| 廠商: | Conexant Systems, Inc. |

| 英文描述: | ATM Transmitter/Receiver with UTOPIA Interface |

| 中文描述: | 自動(dòng)柜員機(jī)發(fā)射機(jī)/接收機(jī)的UTOPIA接口 |

| 文件頁數(shù): | 97/161頁 |

| 文件大?。?/td> | 1832K |

| 代理商: | 28222-14 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁當(dāng)前第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

CN8223

3.0 Registers

ATM Transmitter/Receiver with UTOPIA Interface

3.3 Configuration Control Registers

100046C

Conexant

3-11

Enables the internal HDLC data link receiver and transmitter. Programming for the

HDLC data link is described in

Section 2.8

.

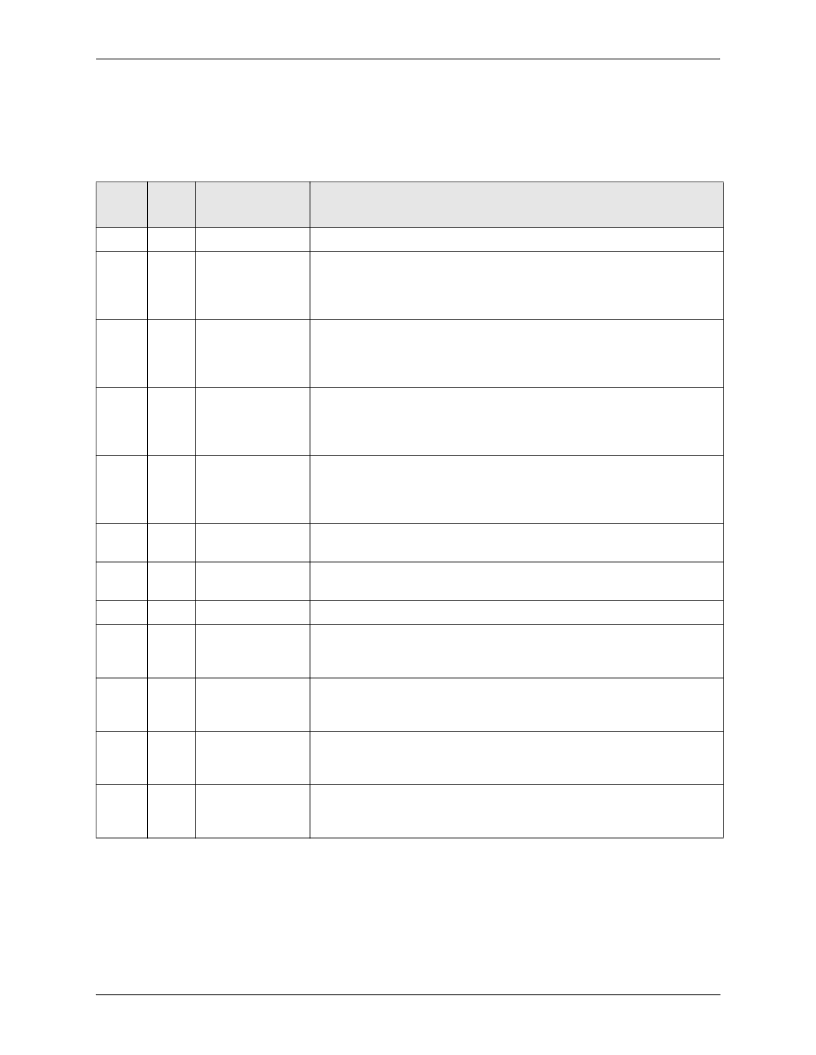

0x31

—

CONFIG_5 (Configuration Control Register 5)

The CONFIG_5 register is located at address 0x31 and controls miscellaneous functions. Bits 3

–

0 are control

bits which can be written and read. Bits 10, 9, and 8 are read-only status bits.

Bit

Field

Size

Name

Description

15

–

11

5

Reserved

Set to 0.

10

1

Receive G1 Bit 5

Indicates the value of the RDI qualifier bit being received in the G1 octet of the

STS-3c/STM-1 frame. This bit would be used in conjunction with bit 4 in the

LINE_STATUS register [0x38] to determine the type of RDI (Path Yellow) being

received.

9

1

Receive G1 Bit 6

Indicates the value of the RDI qualifier bit being received in the G1 octet of the

STS-3c/STM-1 frame. This bit would be used in conjunction with bit 4 in the

LINE_STATUS register [0x38] to determine the type of RDI (Path Yellow) being

received.

8

1

Receive G1 Bit 7

Indicates the value of the RDI qualifier bit being received in the G1 octet of the

STS-3c/STM-1 frame. This bit would be used in conjunction with bit 4 in the

LINE_STATUS register [0x38] to determine the type of RDI (Path Yellow) being

received.

7

1

Bt8222: Reserved

for Bt8222B and

higher including the

CN8223: Reset

Set to 0.

In Bt8222 revision B and higher, this bit is a software reset. Writing this bit to 1 has

the same affect as high logic level on pin 118, RESET.

6

1

Set G1 X Bits All-1s

Sets the X bits in the G1 octet of the PLCP overhead to all 1s when this bit is high.

When this bit is low, the X bits will be all 0s.

5

1

Enable HDLC Data

Link

4

1

Reserved

Set to 0.

3

1

Transmit G1 Bit 5

Controls the transmission of the qualified RDI signals in the path status octet (G1) in

SONET/SDH modes. The value written to this bit will be placed in the corresponding

bit of the G1 octet.

2

1

Transmit G1 Bit 6

Controls the transmission of the qualified RDI signals in the path status octet (G1) in

SONET/SDH modes. The value written to this bit will be placed in the corresponding

bit of the G1 octet.

1

1

Enable External

Signal Label

Selects the source for the C2 octet in the path overhead for SONET/SDH formats.

When this bit is low, the C2 octet is internally generated. When this bit is high, the

C2 octet is obtained from the TXOVH inputs.

0

1

Transmit Clock

Select

Selects the clock source for the transmitter circuitry. When this bit is low, the

transmit clock is from the TXCKI or TXCKI_HS± inputs. When this bit is high, the

transmit clock is from the RXCKI or RXCKI_HS± inputs to enable loop timing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28233-11 | ATM Transmitter/Receiver with UTOPIA Interface |

| 28C010TRPDB-12 | 150 x 32 pixel format, LED Backlight available |

| 28C010TRT1DE-15 | 1 Megabit (128K x 8-Bit) EEPROM |

| 28C010TRT1DE-20 | 1 Megabit (128K x 8-Bit) EEPROM |

| 28C010TRT1FB-15 | 1 Megabit (128K x 8-Bit) EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 282222-003 | 制造商:TE Connectivity 功能描述:81044/12-16-2 - Cable Rools/Shrink Tubing |

| 282223-003 | 制造商:TE Connectivity 功能描述:81044/12-16-3 - Cable Rools/Shrink Tubing |

| 282224-003 | 制造商:TE Connectivity 功能描述:81044/12-16-4 - Cable Rools/Shrink Tubing |

| 282224-1 | 功能描述:汽車連接器 ECONOSEAL RCPT CONT .5MM RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類型: 觸點(diǎn)電鍍:Nickel |

| 282225-001 | 制造商:TE Connectivity 功能描述:81044/12-16-5 - Cable Rools/Shrink Tubing |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。