- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F640P3 (Intel Corp.) Intel StrataFlash Embedded Memory PDF資料下載

參數(shù)資料

| 型號(hào): | 28F640P3 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Embedded Memory |

| 中文描述: | 英特爾StrataFlash嵌入式存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 11/82頁(yè) |

| 文件大小: | 749K |

| 代理商: | 28F640P3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

28F6408W30, 28F3204W30, 28F320W30, 28F640W30

Preliminary

5

2.4

Signal Descriptions

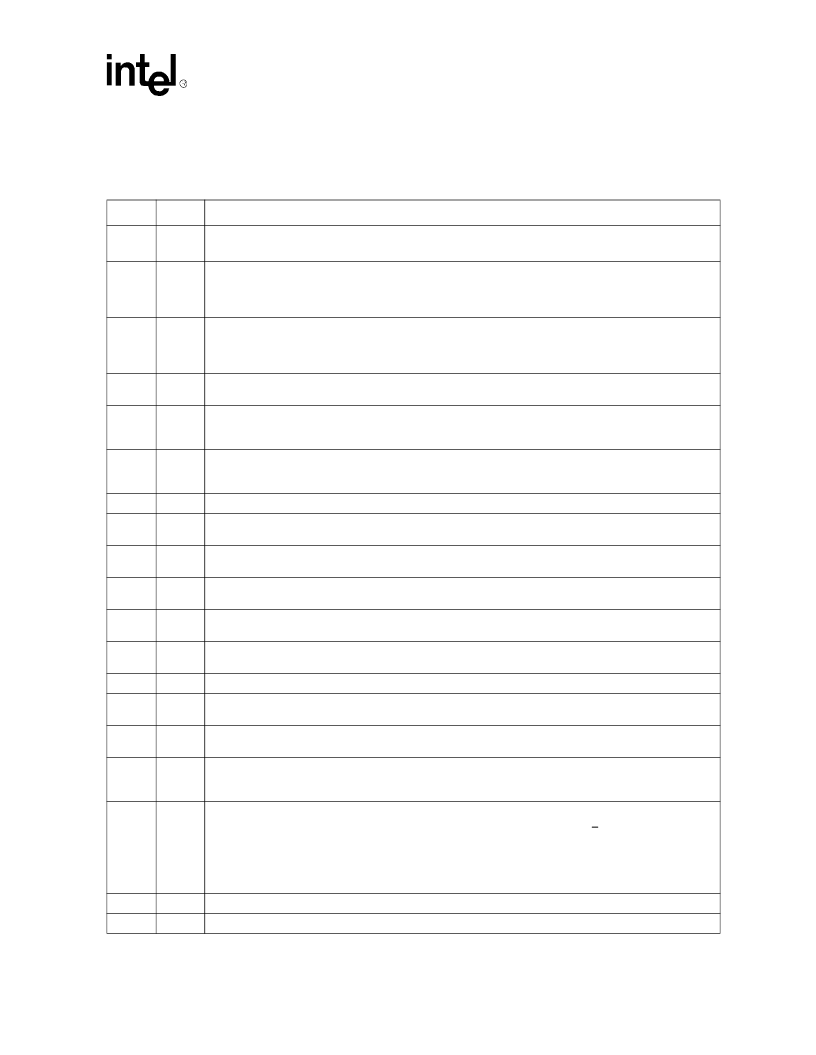

Table 2. Signal Descriptions (Sheet 1 of 2)

Symbol

Type

Name and Function

A

25

–

0

I

ADDRESS:

Device address. Addresses are internally latched during read and write cycles.

32-Mbit flash: A

20

–

0

; 64-Mbit flash: A

21

–

0

; 128-Mbit flash: A

22

–

0

; 4-Mbit SRAM: A

17

–

0

; 8-Mbit SRAM: A

18

–

0

DQ

15

–

0

I/O

DATA INPUT/OUTPUTS:

Inputs data and commands during write cycles, outputs data during query, id

reads, memory, status register, protection register, and configuration code reads. Data signals float when

the chip or outputs are deselected. Data is internally latched during writes. Query accesses and status

register accesses use DQ

0

–

DQ

7

. All other accesses use DQ

0

–

DQ

15

.

ADV#

I

FLASH ADDRESS VALID:

Internally latches addresses. In page mode, addresses are internally latched on

the rising edge of ADV#. In burst mode, address internally latched on the rising edge of ADV# or rising/

falling edge of CLK, whichever occurs first. Connect ADV# to GND when the flash device is operating in

asynchronous mode only.

CE#

I

FLASH CHIP ENABLE:

Enables/disables flash device. CE#-low enables the device. CE#-high disables the

device and places the device into standby mode. CE# high places data and WAIT signals at a High-Z level.

S-CS

1

#

I

SRAM CHIP SELECT1:

Activates the SRAM internal control logic, input buffers, decoders and sense

amplifiers. S-CS

1

# is active low. S-CS

1

# high deselects the SRAM memory device and reduces power

consumption to standby levels.

S-CS

2

I

SRAM CHIP SELECT2:

Activates the SRAM internal control logic, input buffers, decoders and sense

amplifiers. S-CS

2

is active high. S-CS

2

low deselects the SRAM memory device and reduces power

consumption to standby levels.

CLK

I

FLASH CLOCK:

Synchronizes the device to the system bus frequency. (Used only in burst mode.)

OE#

I

FLASH OUTPUT ENABLE:

Enables/disables device output buffers. OE# low enables the device output

buffers. OE# high disables the device output buffers and places all outputs at a High-Z level.

S-OE#

I

SRAM OUTPUT ENABLE:

Activates the SRAM outputs through the data buffers during a read operation.

S-OE# is active low.

RST#

I

FLASH RESET:

Enables/disables device operation. RST# low initializes internal circuitry and disables

device operation. RST# high enables device operation.

WAIT

O

FLASH WAIT:

Indicates valid data in burst read mode. WAIT is at High-Z until the configuration register bit

CR.10 is set, which also determines its polarity when asserted.

WE#

I

FLASH WRITE ENABLE:

Enables/disables device write buffers. WE# low enables the device write buffers.

Data is latched on the rising edge of WE#. WE# high disables the device write buffers.

S-WE#

I

SRAM WRITE ENABLE:

Controls writes to the SRAM memory array. S-WE# is active low.

S-UB#

I

SRAM UPPER BYTE ENABLE:

Enables the upper bytes for SRAM (DQ

15-8

). S-UB# is active low. S-UB#

and S-LB# must be tied together to restrict x16 mode.

S-LB#

I

SRAM LOWER BYTE ENABLE:

Enables the lower bytes for SRAM (DQ

7-0

). S-LB# is active low. S-UB#

and S-LB# must be tied together to restrict x16 mode.

WP#

I

FLASH WRITE PROTECT:

Enables/disables the device lock-down function. WP# low enables the lock-

down mechanism and blocks marked lock-down cannot be unlocked by system software. WP# high

disables the lock-down mechanism and blocks marked lock-down can be unlocked by system software.

V

PP

Pwr

FLASH PROGRAM/ERASE POWER:

Hardware erase and program protection. A valid V

PP

voltage on this

ball allows erase or programming. Memory contents cannot be altered when V

PP

< V

PPLK

. Block erase and

program at invalid V

PP

voltages should not be attempted. Set V

PP

= V

CC

for in-system read, program, and

erase operations. V

PP

must remain above V

PP1

Min to perform in-system operations. V

PP2

can be applied to

main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles.

V

PP

can be V

PP2

for a

cumulative total, not to exceed 80 hours maximum. Extended use of this ball at V

PP2

may reduce block

cycling capability.

V

CC

Pwr

FLASH POWER SUPPLY:

Flash operations at invalid V

CC

voltages should not be attempted.

V

CCQ

Pwr

FLASH OUTPUT POWER SUPPLY:

Enables all input and output signals to be driven at V

CCQ

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F320C3 | 3 Volt Advanced Boot Block Flash Memory(3 V 高級(jí)快速引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F800C3 | 3 Volt Advanced Boot Block Flash Memory(3 V 高級(jí)快速引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F160C3 | 3 Volt Advanced Boot Block Flash Memory(3 V 高級(jí)快速引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F320D18 | 1.8 Volt Intel Dual-Plane Flash Memory(1.8 V Intel 雙平面閃速存儲(chǔ)器) |

| 28F320J5 | 5 Volt Intel StrataFlash Memory(5 V 32M位英特爾StrataFlash存儲(chǔ)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F640W30 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F650 | 制造商:Cinch Connectors 功能描述:1 Lug Terminal Strip |

| 28F651 | 制造商:Cinch Connectors 功能描述:2 Lug Terminal Strip |

| 28F652 | 制造商:Cinch Connectors 功能描述:3 Lug Terminal Strip |

| 28F653 | 制造商:Cinch Connectors 功能描述:4 Lug Terminal Strip |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。