- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371466 > 2N60B (Fairchild Semiconductor Corporation) 600V N-Channel MOSFET PDF資料下載

參數(shù)資料

| 型號: | 2N60B |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | 600V N-Channel MOSFET |

| 中文描述: | 600V的N溝道MOSFET |

| 文件頁數(shù): | 1/9頁 |

| 文件大?。?/td> | 647K |

| 代理商: | 2N60B |

2001 Fairchild Semiconductor Corporation

November 2001

Rev. B, November 2001

S

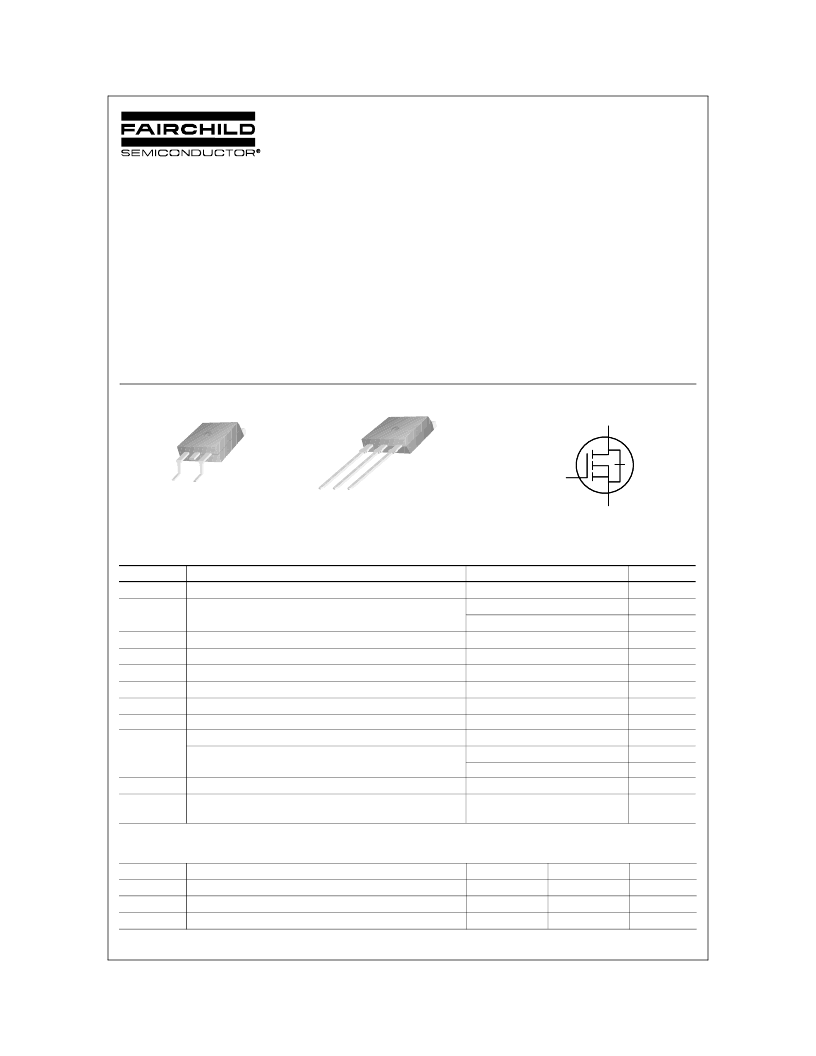

SSW2N60B / SSI2N60B

600V N-Channel MOSFET

General Description

These N-Channel enhancement mode power field effect

transistors are produced using Fairchild’s proprietary,

planar, DMOS technology.

This advanced technology has been especially tailored to

minimize on-state resistance, provide superior switching

performance, and withstand high energy pulse in the

avalanche and commutation mode. These devices are well

suited for high efficiency switch mode power supplies.

Features

2.0A, 600V, R

DS(on)

= 5.0

@V

GS

= 10 V

Low gate charge ( typical 12.5 nC)

Low Crss ( typical 7.6 pF)

Fast switching

100% avalanche tested

Improved dv/dt capability

Absolute Maximum Ratings

T

C

= 25°C unless otherwise noted

Thermal Characteristics

Symbol

V

DSS

I

D

Parameter

SSW2N60B / SSI2N60B

600

2.0

1.3

6.0

±

30

120

2.0

5.4

5.5

3.13

54

0.43

-55 to +150

Units

V

A

A

A

V

mJ

A

mJ

V/ns

W

W

W/°C

°C

Drain-Source Voltage

Drain Current

- Continuous (T

C

= 25°C)

- Continuous (T

C

= 100°C)

- Pulsed

I

DM

V

GSS

E

AS

I

AR

E

AR

dv/dt

P

D

Drain Current

Gate-Source Voltage

Single Pulsed Avalanche Energy

Avalanche Current

Repetitive Avalanche Energy

Peak Diode Recovery dv/dt

Power Dissipation (T

A

= 25°C) *

Power Dissipation (T

C

= 25°C)

(Note 1)

(Note 2)

(Note 1)

(Note 1)

(Note 3)

- Derate above 25°C

T

J

, T

stg

Operating and Storage Temperature Range

Maximum lead temperature for soldering purposes,

1/8

"

from case for 5 seconds

T

L

300

°C

Symbol

R

θ

JC

R

θ

JA

R

θ

JA

* When mounted on the minimum pad size recommended (PCB Mount)

Parameter

Typ

--

--

--

Max

2.32

40

62.5

Units

°C

/

W

°C

/

W

°C

/

W

Thermal Resistance, Junction-to-Case

Thermal Resistance, Junction-to-Ambient *

Thermal Resistance, Junction-to-Ambient

●

●

●

●

●

●

▲

!

S

!

!

!

D

G

D

2

-PAK

SSW Series

I

2

-PAK

SSI Series

G

S

D

G

S

D

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 2N6116 | PROGRAMMABLE UNIJUNCTION TRANSISTOR|TO-18 |

| 2N6117 | PROGRAMMABLE UNIJUNCTION TRANSISTOR|TO-18 |

| 2N6118 | PROGRAMMABLE UNIJUNCTION TRANSISTOR|TO-18 |

| 2N6137 | Military Planar TO-18 Hermetic |

| 2N6147 | SILICON BIDIRECTIOANAL TRIODE THYRISTORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 2N60G-T2Q-T | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:2A, 600V N-CHANNEL POWER MOSFET |

| 2N60G-T60-K | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:2A, 600V N-CHANNEL POWER MOSFET |

| 2N60G-TA3-T | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:2A, 600V N-CHANNEL POWER MOSFET |

| 2N60G-TF1-T | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:2A, 600V N-CHANNEL POWER MOSFET |

| 2N60G-TF3-T | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:2A, 600V N-CHANNEL POWER MOSFET |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。