- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄33761 > 42S16400A (Integrated Silicon Solution, Inc.) 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | 42S16400A |

| 廠商: | Integrated Silicon Solution, Inc. |

| 英文描述: | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 1梅格位× 16位× 4銀行(64兆位)同步動(dòng)態(tài)RAM |

| 文件頁(yè)數(shù): | 1/55頁(yè) |

| 文件大小: | 472K |

| 代理商: | 42S16400A |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

1

Rev.C

04/16/03

IS42S16400A

ISSI

Copyright 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no

liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on

any published information and before placing orders for products.

FEATURES

Clock frequency:166, 133, 100 MHz

Fully synchronous; all signals referenced to a

positive clock edge

Internal bank for hiding row access/precharge

Single 3.3V power supply

LVTTL interface

Programmable burst length

– (1, 2, 4, 8, full page)

Programmable burst sequence:

Sequential/Interleave

Self refresh modes

4096 refresh cycles every 64 ms

Random column address every clock cycle

Programmable

CAS latency (2, 3 clocks)

Burst read/write and burst read/single write

operations capability

Burst termination by burst stop and precharge

command

Byte controlled by LDQM and UDQM

Industrial temperature availability

(133MHz, 100MHz)

Package: 400-mil 54-pin TSOP II,

a lead-free package is available.

OVERVIEW

ISSI's64MbSynchronousDRAMIS42S16400Aisorganized

as 1,048,576 bits x 16-bit x 4-bank for improved

performance. The synchronous DRAMs achieve high-speed

data transfer using pipeline architecture. All inputs and

outputs signals refer to the rising edge of the clock input.

1 Meg Bits x 16 Bits x 4 Banks (64-MBIT)

SYNCHRONOUS DYNAMIC RAM

April 2003

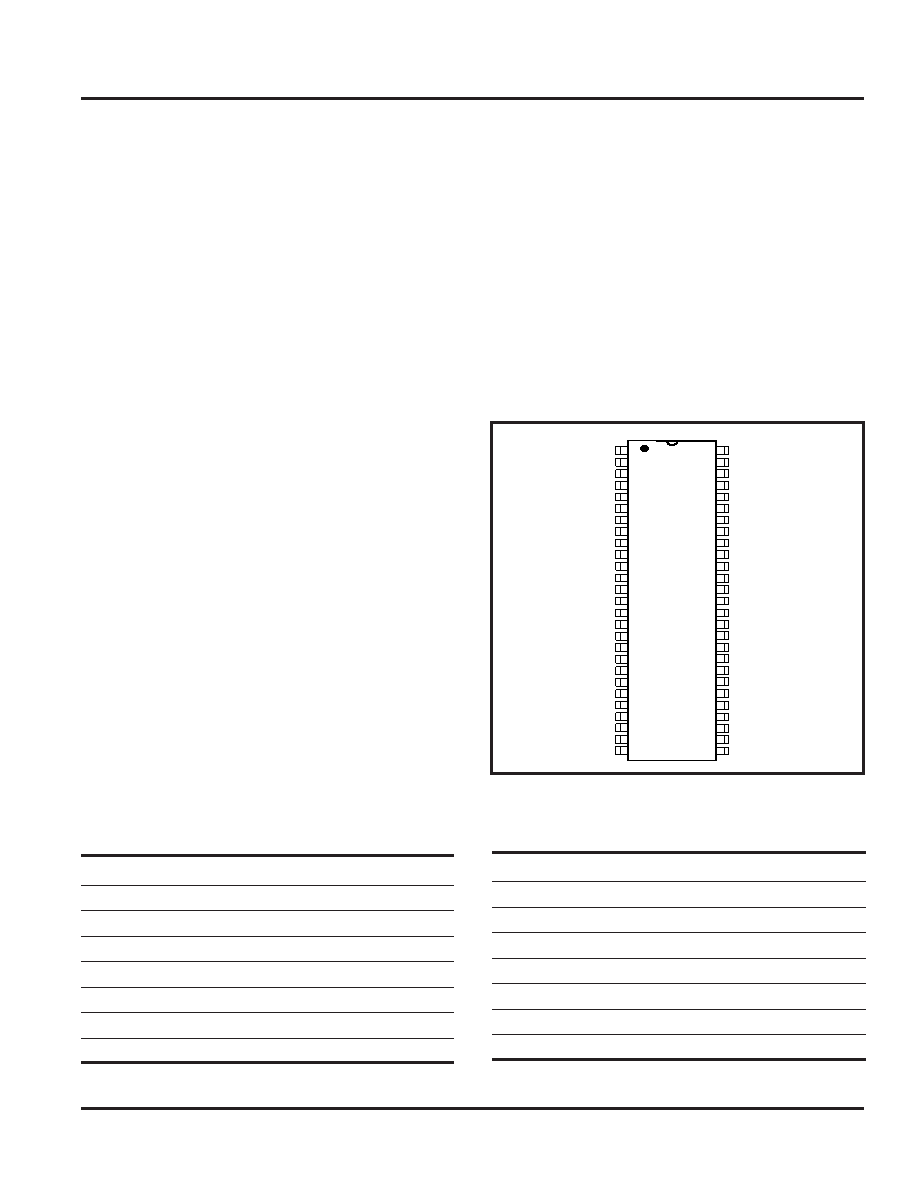

PIN CONFIGURATIONS

54-Pin TSOP (Type II)

VCC

I/O0

VCCQ

I/O1

I/O2

GNDQ

I/O3

I/O4

VCCQ

I/O5

I/O6

GNDQ

I/O7

VCC

LDQM

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

GND

I/O15

GNDQ

I/O14

I/O13

VCCQ

I/O12

I/O11

GNDQ

I/O10

I/O9

VCCQ

I/O8

GND

NC

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

GND

PIN DESCRIPTIONS

A0-A11

Address Input

BA0, BA1

Bank Select Address

I/O0 to I/O15

Data I/O

CLK

System Clock Input

CKE

Clock Enable

CS

Chip Select

RAS

Row Address Strobe Command

CAS

Column Address Strobe Command

WE

Write Enable

LDQM

Lower Bye, Input/Output Mask

UDQM

Upper Bye, Input/Output Mask

Vcc

Power

GND

Ground

VccQ

Power Supply for I/O Pin

GNDQ

Ground for I/O Pin

NC

No Connection

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 42S16800A | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| 42S32200 | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 4300-000 | EMI/RFI FILTER Hermetically Sealed |

| 4300-000LF | |

| 4300-001 | EMI/RFI FILTER Hermetically Sealed |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 42S16400B-6TLTR | 制造商:Integrated Silicon Solution Inc 功能描述: |

| 42S16800A | 制造商:ISSI 制造商全稱(chēng):Integrated Silicon Solution, Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| 42S16800L | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:3.3 V OPERATION 16 M-BIT DYNAMIC RAM 2 M-WORD BY 8-BIT, FAST PAGE MODE |

| 42S16800L-A60 | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:3.3 V OPERATION 16 M-BIT DYNAMIC RAM 2 M-WORD BY 8-BIT, FAST PAGE MODE |

| 42S16800L-A70 | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:3.3 V OPERATION 16 M-BIT DYNAMIC RAM 2 M-WORD BY 8-BIT, FAST PAGE MODE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。