- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄24774 > 935086530518 (NXP SEMICONDUCTORS) 8-BIT, 16 MHz, MICROCONTROLLER, PQCC68 PDF資料下載

參數(shù)資料

| 型號(hào): | 935086530518 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 16 MHz, MICROCONTROLLER, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁(yè)數(shù): | 52/112頁(yè) |

| 文件大?。?/td> | 693K |

| 代理商: | 935086530518 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)

1996 Jun 27

44

Philips Semiconductors

Product specication

8-bit microcontroller with on-chip CAN

P8xC592

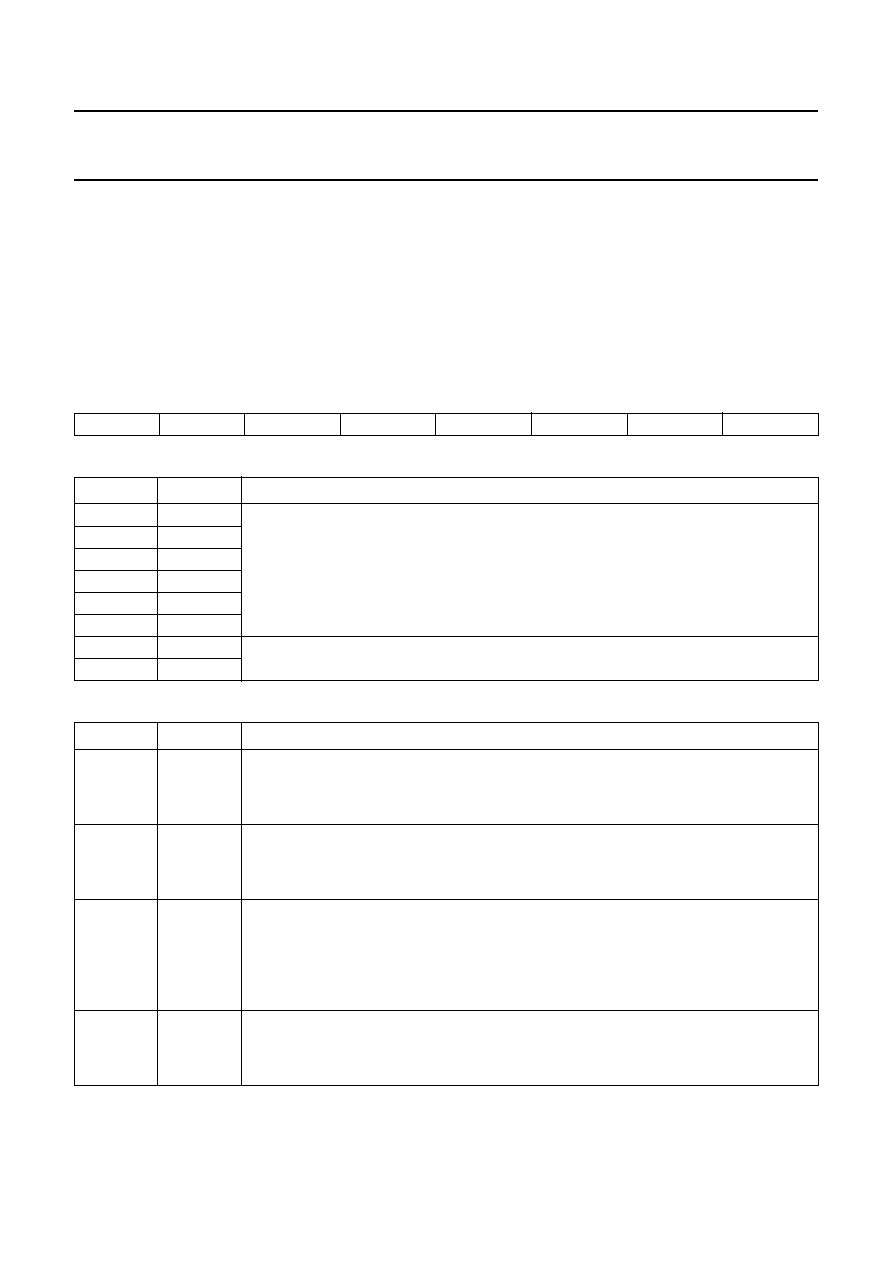

13.5.11 OUTPUT CONTROL REGISTER (OCR)

The Output Control Register allows, under software

control, the set-up of different output driver configurations.

This register can be accessed (read/write) if the Reset

Request bit is set HIGH (present). If the CAN-controller is

in the sleep mode (Sleep = HIGH) a recessive level is

output on the CTX0 and CTX1 pins. If the CAN-controller

is in the reset state (Reset Request = HIGH) the output

drivers are floating.

Tables 50 and 51, show the relationship between the bits

of the Output Control Register and the two serial output

pins CTX0 and CTX1 of the P8xC592 CAN-controller,

connected to the serial bus (see Fig.14).

Table 49 Output Control Register (address 8)

Table 50 Description of the OCR bits

Table 51 Description of the Output Mode bits

7

6

543210

OCTP1

OCTN1

OCPOL1

OCTP0

OCTN0

OCPOL0

OCMODE1

OCMODE0

BIT

SYMBOL

FUNCTION

7

OCTP1

See Tables 51 and 52.

6

OCTN1

5

OCPOL1

4

OCTP0

3

OCTN0

2

OCPOL0

1

OCMODE1 Output Mode.

These bits select the output mode; see Table 51.

0

OCMODE0

OCMODE1 OCMODE0

DESCRIPTION

10

Normal Output Mode. The bit sequence (TXD) is sent via CTX0, CTX1. TXD is the data

bit to be transmitted. The voltage levels on the output driver pins CTX0 and CTX1 depend

on both the driver characteristic programmed by OCTPx, OCTNx (oat, pull-up, pull-down,

push-pull) and the output polarity programmed by OCPOLx (see Fig.17).

11

Clock Output Mode. For the CTX0 pin this is the same as in Normal Output Mode

(CTX0: bit sequence). However, the data stream to CTX1 is replaced by the transmit clock

(TXCLK). The rising edge of the transmit clock (non-inverted) marks the beginning of a bit

period. The clock pulse width is tSCL.

00

Bi-phase Output Mode. In contrast to Normal Output Mode the bit representation is time

variant and toggled. If the bus controllers are galvanically decoupled from the bus-line by a

transformer, the bit stream is not allowed to contain a DC component. This is achieved by

the following scheme. During recessive bits all outputs are deactivated (oating). Dominant

bits are sent alternately on CTX0 and CTX1, i.e. the rst dominant bit is sent on CTX0, the

second is sent on CTX1, and the third one is sent on CTX0 again, etc.

01

Test Output Mode. For the CTX0 pin this is the same as in Normal Output Mode

(CTX0: bit sequence). To measure the delay time of the transmitter and receiver this mode

connects the output of the input comparator (COMP OUT) with the input of the output driver

CTX1. This mode is used for production testing only.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935266795557 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC68 |

| 935086530512 | 8-BIT, 16 MHz, MICROCONTROLLER, PQCC68 |

| 935210470512 | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQCC68 |

| 935089010512 | 8-BIT, 16 MHz, MICROCONTROLLER, PQCC68 |

| 935085020512 | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935087-000 | 制造商:TE Connectivity 功能描述:301A511-51-05/164-0 - Bulk |

| 935087N001 | 制造商:TE Connectivity 功能描述:301A511-51-05/164-CS7092 制造商:TE Connectivity 功能描述:301A511-51-05/164-CS7092 - Bulk |

| 9350DC-200-0GZZZA | 制造商:Siemens 功能描述: |

| 9350DC-200-0ZZZTA | 制造商:Siemens 功能描述: |

| 9350DC-200-0ZZZZA | 制造商:Siemens 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。