- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24776 > 935167560557 (NXP SEMICONDUCTORS) 8-BIT, 16 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | 935167560557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 14 X 20 X 2.70 MM, PLASTIC, QFP-80 |

| 文件頁數(shù): | 106/112頁 |

| 文件大小: | 707K |

| 代理商: | 935167560557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁當(dāng)前第106頁第107頁第108頁第109頁第110頁第111頁第112頁

1996 Jun 27

93

Philips Semiconductors

Product specication

8-bit microcontroller with on-chip CAN

P8xCE598

22.1.2

CALCULATING THE MAXIMUM BIT-TIME

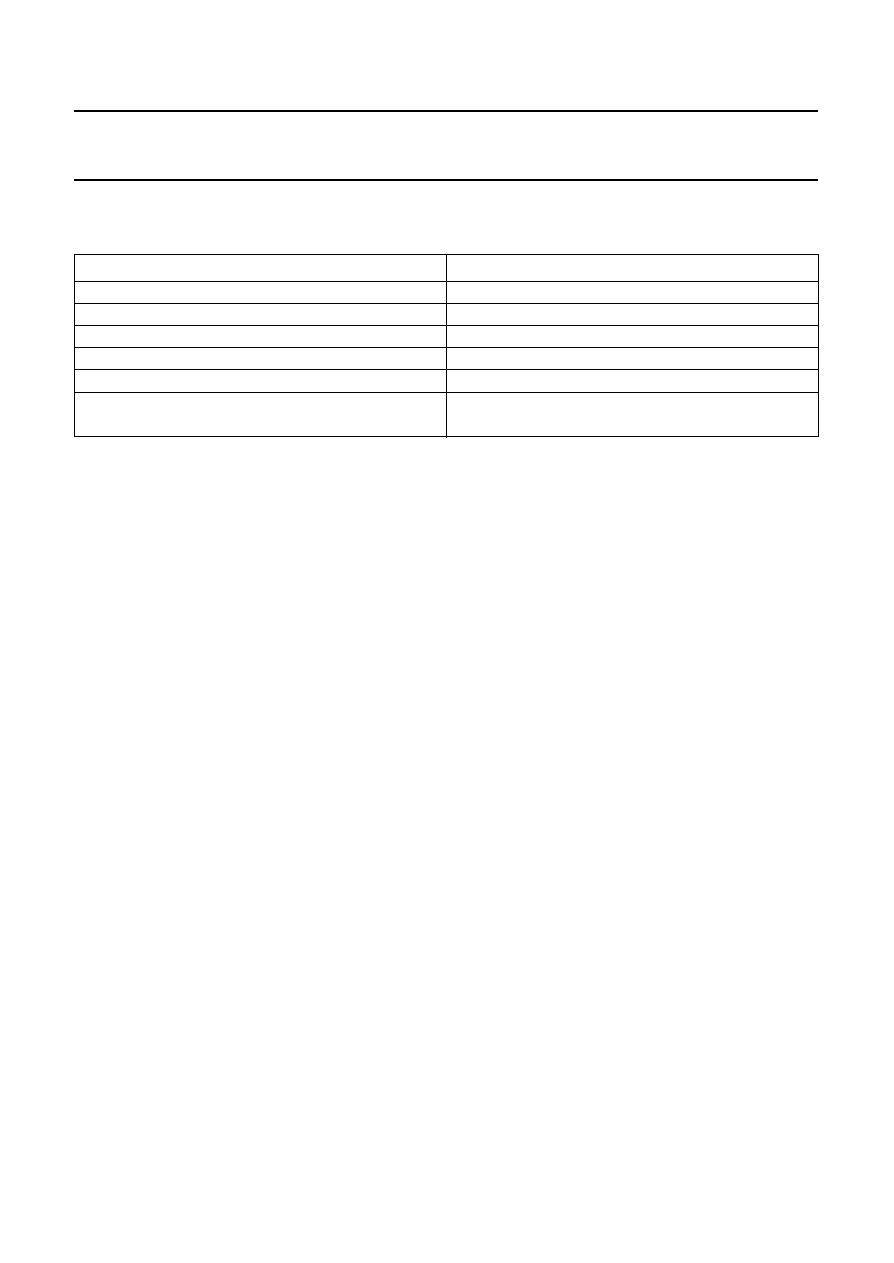

Table 93 Example for calculating the maximum bit-time

STATEMENT

COMMENTS

tMAX TRANSFER TIME = 10 ms

assumption.

nDATA BYTES, WORST CASE = 6

longest message in that network; assumption.

nDATA BYTES = 4

‘our message’; assumption.

nBIT MAX LATENCY ≤ 130

using Equations (3) and (4).

nMESSAGE ≤ 92

using Equation (2).

using Equation (1).

t

BIT

10 ms

130

92

+

()

-----------------------------

0.045 ms

45

s

=

≤

22.2

Connecting a P8xCE598 to a bus line

(physical layer)

22.2.1

ON-CHIP TRANSCEIVER

The P8xCE598 features an on-chip differential transceiver

including output driver and input comparator both being

configurable (see Fig.37). Therefore it supports many

types of common transmission media such as:

Single wire bus line

Two-wire bus line (differential)

Optical cable bus line.

The P8xCE598 can directly drive a differential bus line.

An example is given in Fig.38 for a bus line having a

characteristic impedance of 120

. Direct interfacing to

the bus line is well suited for applications with limited

requirements concerning electromagnetic susceptibility,

wiring failure tolerance and protection against transients.

22.2.2

TRANSCEIVER FOR IN-VEHICLE COMMUNICATION

Fig.39 shows a versatile transceiver implementation

designed for automotive applications. It features a bit rate

of up to 1 Mbit/s and dissipates low power during standby

(1.4 mA). Thus it is suitable also for applications requiring

a Sleep mode function with system activation via the bus

line. The transceiver provides and extended common

mode range for high electromagnetic susceptibility

performance.

Two external driver transistors amplify the output current

to 35 mA typically and provide protection against

overvoltage conditions on the bus line (e.g. due to an

accidental short-circuit between a bus wire and battery

voltage). The serial diodes prevent in combination with the

transistors the bus from being blocked in case of a bus not

powered. More than 32 nodes may be connected to the

bus line.

22.2.3

DETECTION AND HANDLING OF BUS WIRING

FAILURES

Using the P8xCE598 a superior wiring failure tolerance

and detection performance can be achieved. This requires

both bus lines to be mutually decoupled as shown in

Fig.40. Each bus wire is based separately to a reference

voltage of 1

2AVDD.

The diodes suppress reverse current in case of a

termination circuit being not properly powered or a bus line

being short i.e. to a voltage higher than 5 V. Applying this

bus termination circuit the following wiring failures on the

bus are detectable and can be handled:

Interruption of one bus wire at any location.

Short-circuit of one bus wire to ground or battery

voltage.

Short-circuit between the bus wires.

A bus failure can be detected e.g. by a drop out of a status

message, regularly being transmitted on the bus. If a bus

wire is corrupted the following actions have to be taken:

Switch the corresponding comparator input over to a

reference voltage of 1

2AVDD.

Disable the corresponding output driver stage.

As a consequence communication will continue on that

bus wire not being corrupted. The required reference

voltage and the switches for the comparator inputs are

provided on-chip. An output driver stage can be disabled

by reconfiguration of the on-chip output driver

(reprogramming of the Output Control Register of the

P8xCE598; see Section 13.5.11, Table 51). To find out

which of the bus wires is corrupted a heuristic method is

applied.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935165760551 | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP80 |

| 0673.400 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673.500 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673.600 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673.800 | Axial Lead and Cartridge Fuses - Glass Body |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 93516-PIX | 制造商:FCI 功能描述: |

| 93517-090001 | 制造商:FCI 功能描述:PCMCIA REV CARD FRAME 9P |

| 93517-150000 | 制造商:FCI 功能描述: |

| 93518097J | 制造商:Fiskars Brands Inc 功能描述:Fiskars 45mm Rotary Blades - Pinking (Fits Models 195800/154570/19680/19583) (Fr |

| 935181002005 | 功能描述:電容套件 HiTmpSilCap Kit 0402 1nF 10nF 33nF BD11V RoHS:否 制造商:Nichicon 電容范圍:10 uF to 680 uF 公差范圍: 電壓范圍:6.3 V to 25 V 產(chǎn)品:Aluminum Organic Polymer Capacitor Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。