- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36334 > 935242210551 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP160 PDF資料下載

參數(shù)資料

| 型號: | 935242210551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 封裝: | PLASTIC, SOT-322, QFP-160 |

| 文件頁數(shù): | 76/147頁 |

| 文件大?。?/td> | 526K |

| 代理商: | 935242210551 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當前第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁

1998 Apr 09

34

Philips Semiconductors

Product specication

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

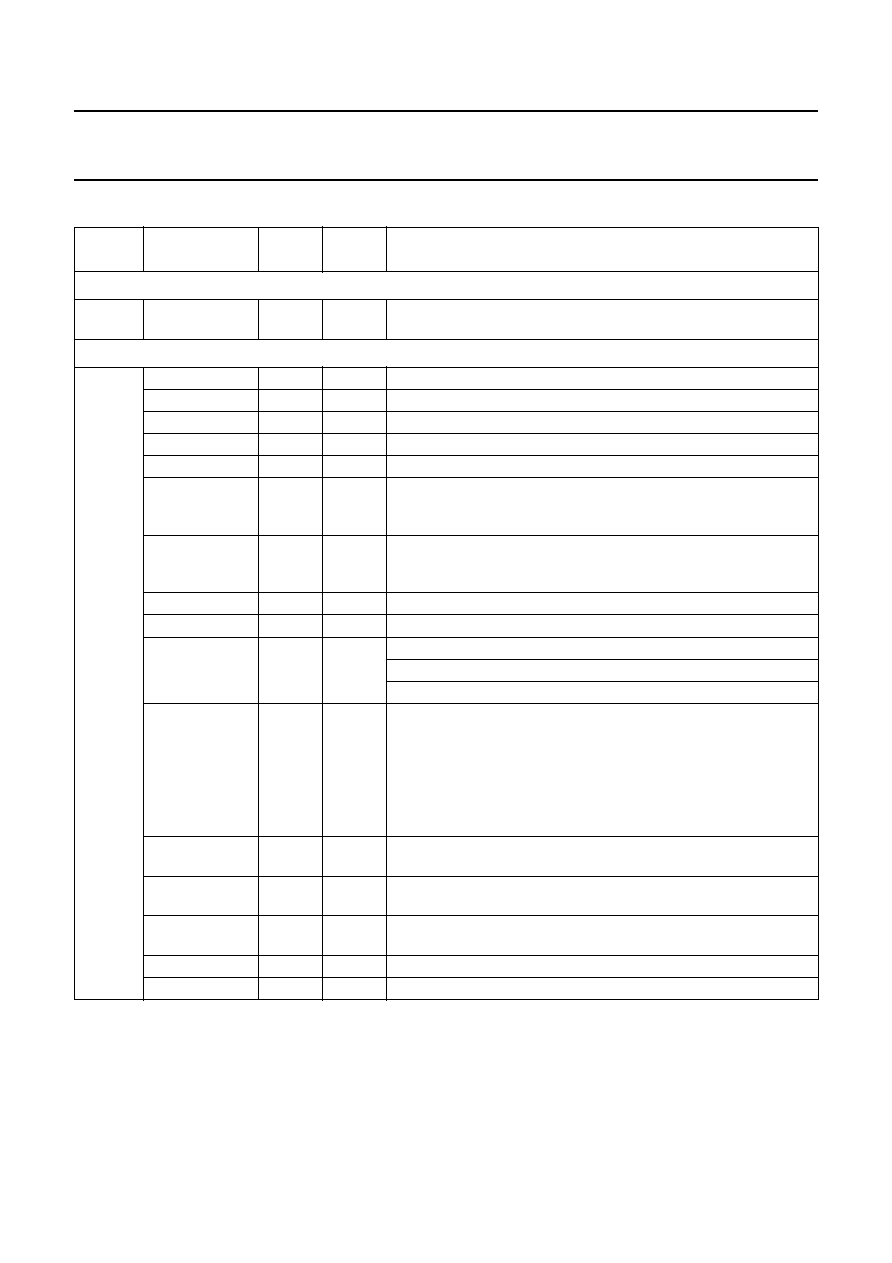

Table 11 Main control register 2

OFFSET

(HEX)

NAME

BIT

TYPE

DESCRIPTION

Mask word

100

M15 to M00

31 to 16

RW

16-bit mask word for bit-selective writes to the control word; when

read this bits always returns logic 0

Control word

100

RPS_SIG4

15

RW

RPS Signal 4

RPS_SIG3

14

RW

RPS Signal 3

RPS_SIG2

13

RW

RPS Signal 2

RPS_SIG1

12

RW

RPS Signal 1

RPS_SIG0

11

RW

RPS Signal 0

UPLD_D1_B

10

RW

Upload ‘Video DATA stream handling at port D1_B (54H)’; see

Table 68. To upload ‘Initial setting of Dual D1 Interface (50H)’, this

bit and bit 9 must be set; see Table 66.

UPLD_D1_A

9

RW

Upload ‘Video DATA stream handling at port D1_A (54H)’; see

Table 67. To upload ‘Initial setting of Dual D1 Interface (50H)’, this

bit and bit 10 must be set; see Table 66.

UPLD_BRS

8

RW

Upload ‘BRS Control Register (58H)’; see Table 69.

7

Reserved; when read this bit always returns a logic 0.

UPLD_HPS_H

6

RW

Upload ‘HPS Horizontal prescale (68H)’; see Table 79.

Upload ‘HPS Horizontal ne-scale (6CH)’; see Table 81.

Upload ‘BCS control (70H)’; see Table 82.

UPLD_HPS_V

5

RW

Upload ‘HPS control (5CH)’; see Table 71.

Upload ‘HPS Vertical scale (60H)’; see Table 72.

Upload ‘HPS Vertical scale and gain (64H)’; see Table 73.

Upload ‘Chroma Key range (74H)’; see Table 86.

Upload ‘HPS Outputs and Formats (78H)’; see Table 87.

Upload ‘Clip control (78H)’; see Table 89.

UPLD_DMA3

4

RW

Upload ‘Video DMA3 registers’; 30H, 34H, 38H, 3CH, 40H, 44H

and 48H (20 to 16).

UPLD_DMA2

3

RW

Upload ‘Video DMA2 registers’; 18H, 1CH, 20H, 24H, 28H, 2CH

and 48H (12 to 8).

UPLD_DMA1

2

RW

Upload ‘Video DMA1 registers’; 00H, 04H, 08H, 0CH, 10H, 14H

and 48H (4 to 0).

UPLD_DEBI

1

RW

Upload ‘DEBI registers’; 88H, 7CH, 80H, 84H and 48H (28 to 26).

UPLD_IIC

0

RW

Upload ‘I2C-bus registers’; (8CH and 90H).

相關PDF資料 |

PDF描述 |

|---|---|

| 935242210557 | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 935262922551 | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 935262922557 | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 935242220551 | SPECIALTY CONSUMER CIRCUIT, PQFP208 |

| 935242220557 | SPECIALTY CONSUMER CIRCUIT, PQFP208 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 935245650125 | 制造商:NXP Semiconductors 功能描述:Inverter 1-Element CMOS 5-Pin TSSOP T/R |

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

| 935252-5 | 制造商:C-H 功能描述:935252-5 |

| 935257650112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY ICSUBS TO 935257650112 |

發(fā)布緊急采購,3分鐘左右您將得到回復。