- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25516 > 954101DGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | 954101DGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.240 INCH, 0.020 INCH PITCH, GREEN, MO-153, TSSOP-56 |

| 文件頁數(shù): | 12/21頁 |

| 文件大小: | 251K |

| 代理商: | 954101DGLFT |

2

Integrated

Circuit

Systems, Inc.

ICS954101

0815F—08/15/05

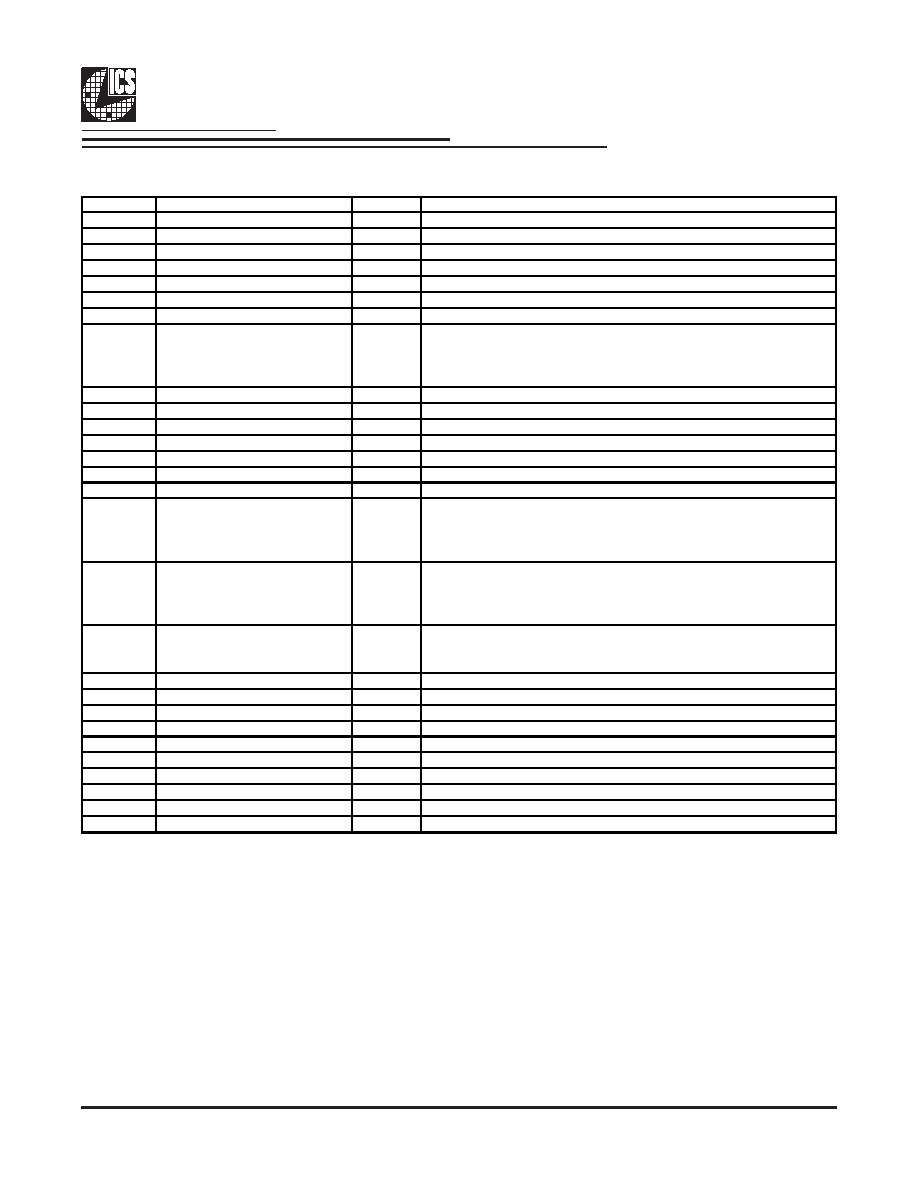

Pin Description

Pin #

PIN NAME

PIN TYPE

DESCRIPTION

1

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

2

GND

PWR

Ground pin.

3

PCICLK3

OUT

PCI clock output.

4

PCICLK4

OUT

PCI clock output.

5

PCICLK5

OUT

PCI clock output.

6

GND

PWR

Ground pin.

7

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

8

ITP_EN/PCICLK_F0

I/O

Free running PCI clock not affected by PCI_STOP#.

ITP_EN: latched input to select pin functionality

1 = CPU_ITP pair

0 = SRC pair

9

PCICLK_F1

OUT

Free running PCI clock not affected by PCI_STOP# .

10

PCICLK_F2

OUT

Free running PCI clock not affected by PCI_STOP# .

11

VDD48

PWR

Power pin for the 48MHz output.3.3V

12

USB_48MHz

OUT

48.00MHz USB clock

13

GND

PWR

Ground pin.

14

DOTT_96MHz

OUT

True clock of differential pair for 96.00MHz DOT clock.

15

DOTC_96MHz

OUT

Complement clock of differential pair for 96.00MHz DOT clock.

16

FS_B/TEST_MODE

IN

3.3V tolerant input for CPU frequency selection. Refer to input electrical

characteristics for Vil_FS and Vih_FS values. TEST_MODE is a real time

input to select between Hi-Z and REF/N divider mode while in test mode.

Refer to Test Clarification Table.

17

Vtt_PwrGd#/PD

IN

Vtt_PwrGd# is an active low input used to determine when latched inputs

are ready to be sampled. PD is an asynchronous active high input pin

used to put the device into a low power state. The internal clocks, PLLs

and the crystal oscillator are stopped.

18

FS_A_410

IN

3.3V tolerant low threshold input for CPU frequency selection. This pin

requires CK410 FSA. Refer to input electrical characteristics for Vil_FS

and Vih_FS threshold values.

19

SRCCLKT1

OUT

True clock of differential SRC clock pair.

20

SRCCLKC1

OUT

Complement clock of differential SRC clock pair.

21

VDDSRC

PWR

Supply for SRC clocks, 3.3V nominal

22

SRCCLKT2

OUT

True clock of differential SRC clock pair.

23

SRCCLKC2

OUT

Complement clock of differential SRC clock pair.

24

SRCCLKT3

OUT

True clock of differential SRC clock pair.

25

SRCCLKC3

OUT

Complement clock of differential SRC clock pair.

26

SRCCLKT4_SATA

OUT

True clock of differential SRC/SATA pair.

27

SRCCLKC4_SATA

OUT

Complement clock of differential SRC/SATA pair.

28

VDDSRC

PWR

Supply for SRC clocks, 3.3V nominal

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 954101YFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954101YGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954119DFLF-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954119DFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954201BG | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 954103-000 | 制造商:TE Connectivity 功能描述:Conn Triaxial 制造商:TE Connectivity 功能描述:D-621-0038CS1271 - Bulk |

| 9541030000 | 制造商:Weidmuller 功能描述:NEXT 30/30/20 3GP PAINTED -EA - Bulk |

| 954-103-5006 | 制造商:Amphenol Corporation 功能描述:SC CONNECTOR, CERAMIC FERRULE, 126UM ANGLE - Bulk 制造商:Amphenol RF 功能描述:Conn SC Adapter Single Mode F/F ST Panel Mount |

| 954103EF | 制造商:Integrated Device Technology Inc 功能描述:954103EF - Rail/Tube |

| 954103EFLN | 制造商:Integrated Device Technology Inc 功能描述:954103EFLN - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。