- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25516 > 954101DGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 954101DGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.240 INCH, 0.020 INCH PITCH, GREEN, MO-153, TSSOP-56 |

| 文件頁(yè)數(shù): | 4/21頁(yè) |

| 文件大?。?/td> | 251K |

| 代理商: | 954101DGLFT |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

12

Integrated

Circuit

Systems, Inc.

ICS954101

0815F—08/15/05

I

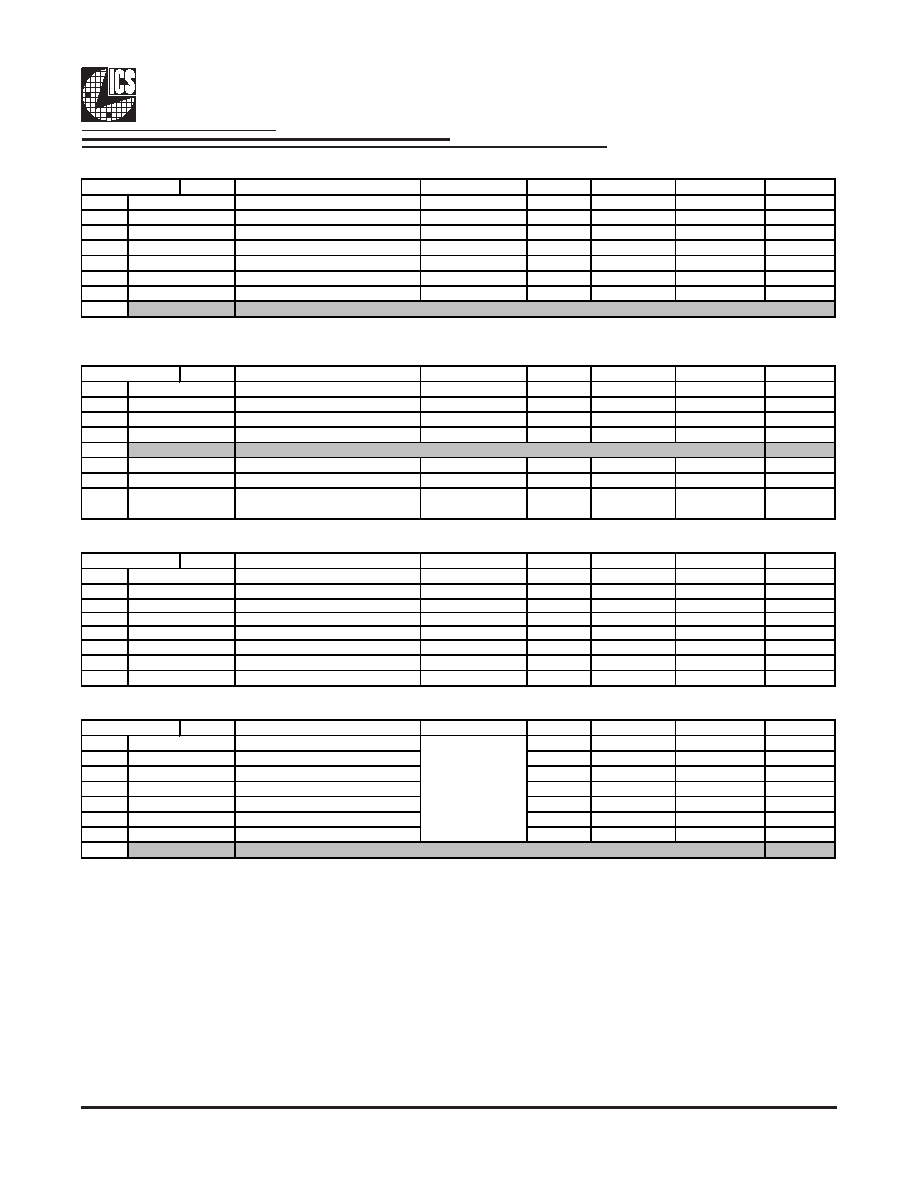

2C Table: Read-Back Register

Pin #

Name

Control Function

Type0

1

PWD

Bit 7

CPUCLK2/RCCLK7 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 6

SRCCLK6 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 5

SRCCLK5 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 4

SRCCLK4 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 3

SRCCLK3 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 2

SRCCLK2 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 1

SRCCLK1 Enable

Output Enable

RW

DISABLE

ENABLE

1

Bit 0

I

2C Table: Spreading and Device Behavior Control Register

Pin #

Name

Control Function

Type0

1

PWD

Bit 7

PCI_F0 Enable

Output Enable

RW

Disable

Enable

1

Bit 6

DOT_96MHz

Output Enable

RW

Disable

Enable

1

Bit 5

USB_48MHz Enable

Output Enable

RW

Disable

Enable

1

Bit 4

REFOUT Enable

Output Enable

RW

Disable

Enable

1

Bit 3

1

Bit 2

CPUT1/CPUC1

Output Enable

RW

Disable

Enable

1

Bit 1

CPUT0/CPUC0

Output Enable

RW

Disable

Enable

1

Bit 0

Spread Spectrum Mode

Spread Off

RW

SPREAD OFF

SPREAD

ON

0

I

2C Table: Output Control Register

Pin #

Name

Control Function

Type0

1

PWD

Bit 7

PCICLK5

Output Enable

RW

Disable

Enable

1

Bit 6

PCICLK4

Output Enable

RW

Disable

Enable

1

Bit 5

PCICLK3

Output Enable

RW

Disable

Enable

1

Bit 4

PCICLK2

Output Enable

RW

Disable

Enable

1

Bit 3

PCICLK1

Output Enable

RW

Disable

Enable

1

Bit 2

PCICLK0

Output Enable

RW

Disable

Enable

1

Bit 1

PCI_F2 Enable

Output Enable

RW

Disable

Enable

1

Bit 0

PCI_F1 Enable

Output Enable

RW

Disable

Enable

1

I

2C Table: Output Control Register

Pin #

Name

Control Function

Type0

1

PWD

Bit 7

CPU_ITP/SRCCLK7

RW

Free-Running

Stoppable

0

Bit 6

SRCCLK6

RW

Free-Running

Stoppable

0

Bit 5

SRCCLK5

RW

Free-Running

Stoppable

0

Bit 4

SRCCLK4

RW

Free-Running

Stoppable

0

Bit 3

SRCCLK3

RW

Free-Running

Stoppable

0

Bit 2

SRCCLK2

RW

Free-Running

Stoppable

0

Bit 1

SRCCLK1

RW

Free-Running

Stoppable

0

Bit 0

0

54

4

3

56

55

30,31

26,27

32,33

9

Byte 0

35,36

32,33

30,31

26,27

24,25

22,23

19,20

Byte 2

5

10

24,25

22,23

19,20

-

43,44

-

40,41

12

52

Byte 3

Free-Running

Control

default:

not affected by

PCI/SRC_STOP

(Byte 6, bit 3)

RESERVED

-

Byte 1

54

14,15

RESERVED

35,35

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 954101YFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954101YGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954119DFLF-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954119DFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954201BG | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 954103-000 | 制造商:TE Connectivity 功能描述:Conn Triaxial 制造商:TE Connectivity 功能描述:D-621-0038CS1271 - Bulk |

| 9541030000 | 制造商:Weidmuller 功能描述:NEXT 30/30/20 3GP PAINTED -EA - Bulk |

| 954-103-5006 | 制造商:Amphenol Corporation 功能描述:SC CONNECTOR, CERAMIC FERRULE, 126UM ANGLE - Bulk 制造商:Amphenol RF 功能描述:Conn SC Adapter Single Mode F/F ST Panel Mount |

| 954103EF | 制造商:Integrated Device Technology Inc 功能描述:954103EF - Rail/Tube |

| 954103EFLN | 制造商:Integrated Device Technology Inc 功能描述:954103EFLN - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。