- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄4347 > A1460A-1PG207C (Microsemi SoC)IC FPGA 6K GATES 207-CPGA PDF資料下載

參數(shù)資料

| 型號(hào): | A1460A-1PG207C |

| 廠商: | Microsemi SoC |

| 文件頁(yè)數(shù): | 4/90頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 6K GATES 207-CPGA |

| 標(biāo)準(zhǔn)包裝: | 10 |

| 系列: | ACT™ 3 |

| LAB/CLB數(shù): | 848 |

| 輸入/輸出數(shù): | 168 |

| 門(mén)數(shù): | 6000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 通孔 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 207-BCPGA |

| 供應(yīng)商設(shè)備封裝: | 207-CPGA(44.96x44.96) |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)

Detailed Specifications

2- 4

R e v ision 3

The I/O module output Y is used to bring Pad signals into the array or to feed the output register back into

the array. This allows the output register to be used in high-speed state machine applications. Side I/O

modules have a dedicated output segment for Y extending into the routing channels above and below

(similar to logic modules). Top/Bottom I/O modules have no dedicated output segment. Signals coming

into the chip from the top or bottom are routed using F-fuses and LVTs (F-fuses and LVTs are explained

in detail in the routing section).

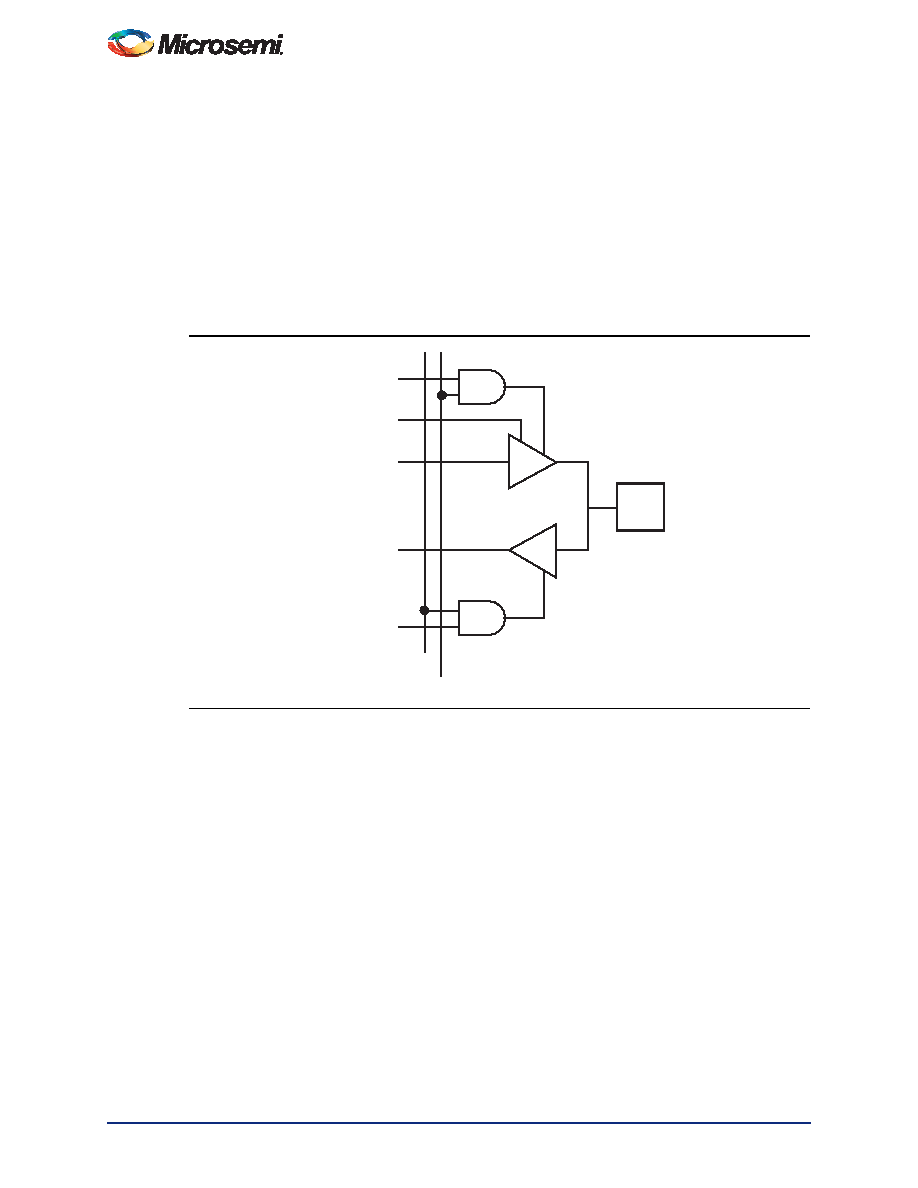

I/O Pad Drivers

All pad drivers are capable of being tristate. Each buffer connects to an associated I/O module with four

signals: OE (Output Enable), IE (Input Enable), DataOut, and DataIn. Certain special signals used only

during programming and test also connect to the pad drivers: OUTEN (global output enable), INEN

(global input enable), and SLEW (individual slew selection). See Figure 2-5.

Special I/Os

The special I/Os are of two types: temporary and permanent. Temporary special I/Os are used during

programming and testing. They function as normal I/Os when the MODE pin is inactive. Permanent

special I/Os are user programmed as either normal I/Os or special I/Os. Their function does not change

once the device has been programmed. The permanent special I/Os consist of the array clock input

buffers (CLKA and CLKB), the hard-wired array clock input buffer (HCLK), the hard-wired I/O clock input

buffer (IOCLK), and the hard-wired I/O register preset/clear input buffer (IOPCL). Their function is

determined by the I/O macros selected.

Clock Networks

The ACT 3 architecture contains four clock networks: two high-performance dedicated clock networks

and two general purpose routed networks. The high-performance networks function up to 200 MHz,

while the general purpose routed networks function up to 150 MHz.

Figure 2-5

Function Diagram for I/O Pad Driver

PAD

OE

SLEW

DATAOUT

DATAIN

IEN

INEN

OUTEN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP4SGX70DF29I4 | IC STRATIX IV FPGA 70K 780FBGA |

| EP4SGX70DF29C3 | IC STRATIX IV FPGA 70K 780FBGA |

| EP1S40F1020C7 | IC STRATIX FPGA 40K LE 1020-FBGA |

| ASC49DRES-S93 | CONN EDGECARD 98POS .100 EYELET |

| EP2S60F672C4 | IC STRATIX II FPGA 60K 672-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A1460A-1PG207M | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 Family 6K Gates 848 Cells 125MHz 0.8um Technology 5V 207-Pin CPGA 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 6K GATES 848 CELLS 125MHZ 0.8UM 5V 207CPGA - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 6K GATES 207-CPGA |

| A1460A-1PG256B | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:HiRel FPGAs |

| A1460A-1PG256C | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:HiRel FPGAs |

| A1460A-1PG256E | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:HiRel FPGAs |

| A1460A-1PG256M | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:HiRel FPGAs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。