- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298744 > A42MX16-2VQ100A (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF資料下載

參數(shù)資料

| 型號: | A42MX16-2VQ100A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件頁數(shù): | 42/120頁 |

| 文件大小: | 854K |

| 代理商: | A42MX16-2VQ100A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

28

4958B–AUTO–11/10

Atmel ATA6285/ATA6286 [Preliminary]

3.7

Clock Generation

3.7.1

Clock Module

The ATA6289 contains a clock module with two internal oscillator types:

FRC: Fast running, programmable, and calibrated RC-oscillator (1MHz/4MHz ±10%)

SRC: Slowly running and calibrated RC-oscillator (90kHz ±10%)

PC1/ECIN0- pin and PD4/ECIN1- pin can be used as input for two different external clocks and

PC1/CLKO-pin as output for the divided system clock. All of these oscillator types and external

input clocks can be selected to generate the system clock (CLK). A special feature of the clock

management is capability of switching between these different clock sources during run time.

This new feature has the advantage, that now the controller can start operation after wakeup

signal with the calibrated internal RC-oscillator and can switch to an external clock as system

clock. A synchronization stage avoids too short clock periods if the clock source or the clock

speed is changed. If an external input clock is selected, a supervisor circuit monitors the external

input and switches automatically to an internal RC-oscillator clock if the external clock source

fails. The ECF-bit indicates the condition of the external input clock monitoring circuit in the

CMSR register. The corresponding monitoring interrupt is executed, if the accessory interrupt

enable bit is set.

In applications that do not require exact timing, it is possible to use the fully integrated RC-oscil-

lators. Both RC-oscillators center frequency tolerance can be calibrated by VCC = 3V/25°C

within ±1% accuracy. The SRC and the Timer0 can work together as a ultra low power Watch-

dog/Interval timer stage.

The clock module is programmable via software with the clock management control register

(CMCR) and the clock prescaler register (CLKPR). The required oscillator configuration can be

selected with the CMM[1..0] bits in the CMCR-register. A system clock prescaler contains a pro-

grammable 7-bit divider stage. This stage divide the system clock by setting the Clock Prescaler

Register (CLKPR), and allows the adjustment of the system clock speed (CLK) and additionally

also the timer clock speed (CLT). This can be used with all clock source options, and it will affect

the clock frequency of the CPU and all synchronous peripherals. CLK

I/O, CLKCPU, and CLKFlash

are divided by a factor as shown in Table 3-10 on page 37.

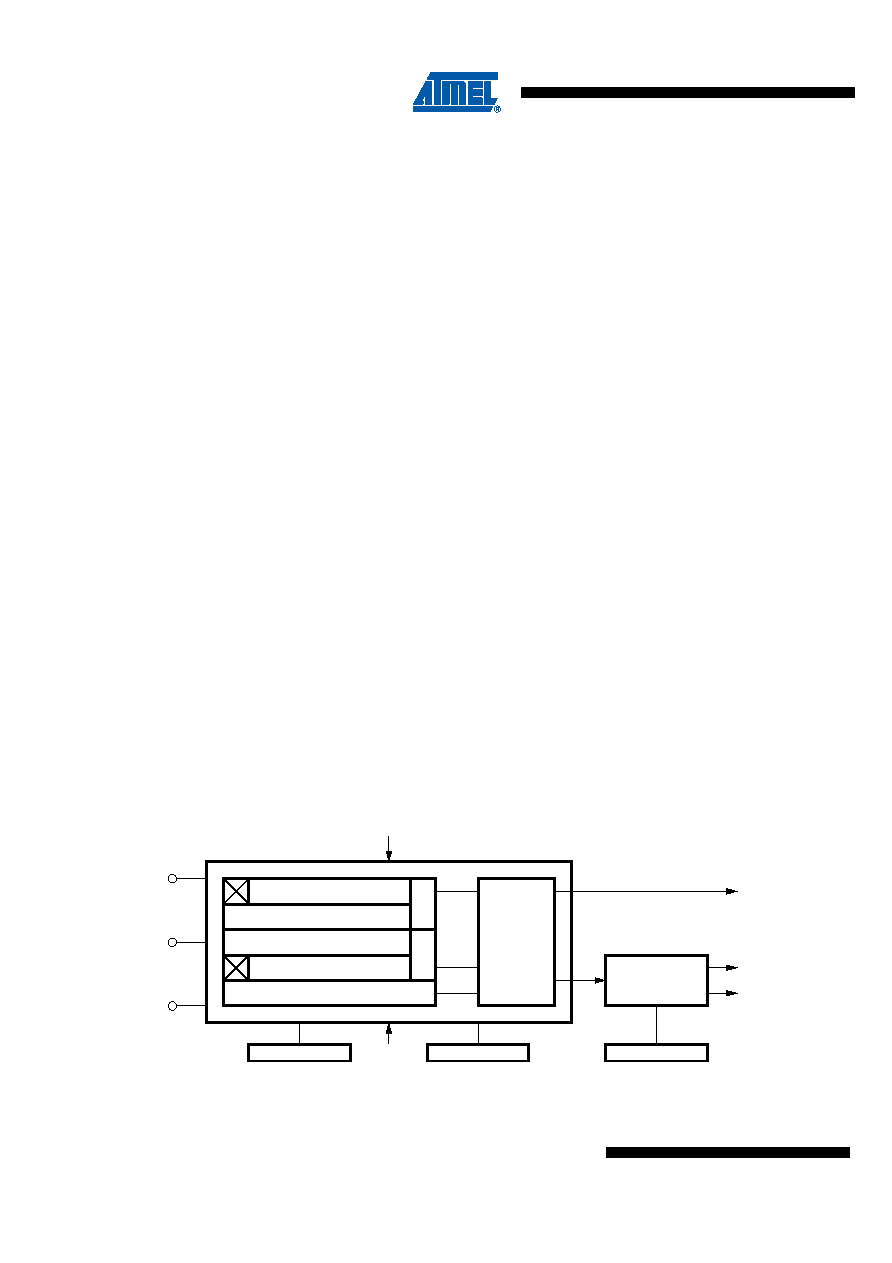

Figure 3-11. Clock Module Unit

SRC-Osc.(Callibrated)

External Clock

Stop

CMSR Register

Fuse option bits

Control

ECF

Stop

Clock Decoder

and

Monitoring

System Clock

Prescaler

FRC

CLK

CLT

SRC

PD4

(ECIN1)

CL

ECL

SRC

FRC-Osc.(Callibrated) Stop

PC0

(ECIN0)

PC1

(CLKO)

CMCR Register

CLKPR Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A42MX16-2VQ100B | 40MX and 42MX FPGA Families |

| A42MX16-2VQ100ES | 40MX and 42MX FPGA Families |

| A42MX16-3PQ100B | 40MX and 42MX FPGA Families |

| A42MX16-3BG100 | 40MX and 42MX FPGA Families |

| A42MX16-3PL100 | 40MX and 42MX FPGA Families |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A42MX16-2VQ100B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-2VQ100ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-2VQ100I | 功能描述:IC FPGA MX SGL CHIP 24K 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A42MX16-2VQ100M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-2VQG100 | 功能描述:IC FPGA MX SGL CHIP 24K 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。