- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17062 > AD9772A-EBZ (Analog Devices Inc)BOARD EVAL FOR AD9772A PDF資料下載

參數(shù)資料

| 型號(hào): | AD9772A-EBZ |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 9/40頁(yè) |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9772A |

| 產(chǎn)品培訓(xùn)模塊: | DAC Architectures |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | TxDAC+® |

| DAC 的數(shù)量: | 1 |

| 位數(shù): | 14 |

| 采樣率(每秒): | 160M |

| 數(shù)據(jù)接口: | 并聯(lián) |

| 設(shè)置時(shí)間: | 11ns |

| DAC 型: | 電流 |

| 工作溫度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9772A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

AD9772A

Rev. C | Page 17 of 40

THEORY OF OPERATION

FUNCTIONAL DESCRIPTION

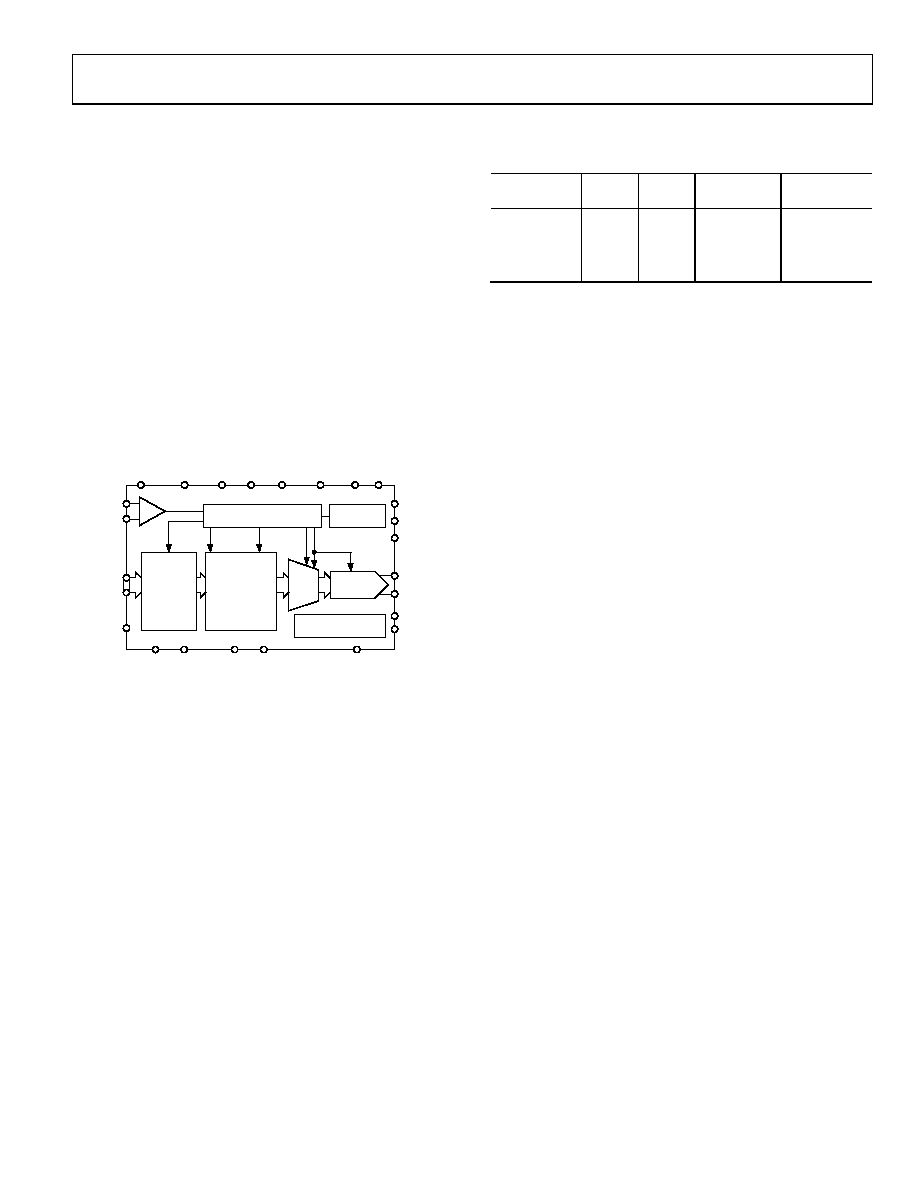

Figure 26 shows a simplified block diagram of the AD9772A.

The AD9772A is a complete 2× oversampling, 14-bit DAC that

includes a 2× interpolation filter, a phase-locked loop (PLL)

clock multiplier, and a 1.20 V band gap voltage reference.

Although the AD9772A digital interface can support input data

rates as high as 160 MSPS, its internal DAC can operate up to

400 MSPS, thus providing direct IF conversion capabilities.

The 14-bit DAC provides two complementary current outputs

whose full-scale current is determined by an external resistor.

The AD9772A features a flexible, low jitter differential clock

input, providing excellent noise rejection while accepting a sine

wave input. An on-chip PLL clock multiplier produces all of the

necessary synchronized clocks from an external reference clock

source. Separate supply inputs are provided for each functional

block to ensure optimum noise and distortion performance. A

sleep mode is also included for power savings.

14-BIT DAC

2× FIR

INTER-

POLATION

FILTER

EDGE-

TRIGGERED

LATCHES

CLOCK DISTRIBUTION

AND MODE SELECT

2× /4×

MUX

CONTROL

FILTER

CONTROL

1× /2×

1×

PLL CLOCK

MULTIPLIER

1.2V REFERENCE

AND CONTROL AMP

AD9772A

CLKCOM CLKVDD MOD0 MOD1 RESET PLLLOCK DIV0 DIV1

CLK+

CLK–

DATA

INPUTS

(DB13 TO

DB0)

SLEEP

DCOM DVDD

ACOM AVDD

REFLO

PLLCOM

LPF

PLLVDD

IOUTA

IOUTB

REFIO

FSADJ

ZERO

STUFF

MUX

0

2253-

026

Figure 26. Simplified Functional Block Diagram

Preceding the 14-bit DAC is a 2× digital interpolation filter that

can be configured for a low-pass (that is, baseband mode) or

high-pass (that is, direct IF mode) response. The input data is

latched into the edge-triggered input latches on the rising edge

of the differential input clock, as shown in Figure 2, and then

interpolated by a factor of 2 by the digital filter. For traditional

baseband applications, the 2× interpolation filter has a low-pass

response. For direct IF applications, the filter response can be

converted into a high-pass response to extract the higher image.

The output data of the 2× interpolation filter can update the

14-bit DAC directly or undergo a zero-stuffing process to increase

the DAC update rate by another factor of 2. This action enhances

the relative signal level and pass-band flatness of the higher

frequency images.

DIGITAL MODES OF OPERATION

The AD9772A features four modes of operation controlled by

the digital inputs, MOD0 and MOD1. MOD0 controls the 2×

digital filter response (that is, low-pass or high-pass), and

MOD1 controls the zero-stuffing option. The appropriate mode

to select (see Table 9) depends on whether the application

requires the reconstruction of a baseband or IF signal.

Table 9. Digital Modes

Digital

Mode

MOD0

MOD1

Digital

Filter

Zero-

Stuffing

Baseband

0

Low

No

Baseband

0

1

Low

Yes

Direct IF

1

0

High

No

Direct IF

1

High

Yes

For applications requiring the highest dynamic range over a

wide bandwidth, users should consider operating the AD9772A

in a baseband mode. Although the zero-stuffing option can be

used in this mode, the ratio of the signal to the image power

will be reduced.

For applications requiring the synthesis of IF signals, users

should consider operating the AD9772A in a direct IF mode. In

this case, the zero-stuffing option should be considered when

synthesizing and selecting IFs beyond the input data rate, fDATA.

If the reconstructed IF falls below fDATA, the zero-stuffing option

may or may not be beneficial. Note that the dynamic range (that

is, SNR/SFDR) can be optimized by disabling the PLL clock

multiplier (that is, by connecting PLLVDD to PLLCOM) and by

using an external low-jitter clock source operating at the DAC

update rate, fDAC.

2× Interpolation Filter Description

The 2× interpolation filter is based on a 43-tap, half-band,

symmetric FIR topology that can be configured for a low- or

high-pass response, depending on the state of the MOD0

control input. The low-pass response is selected with MOD0

low, and the high-pass response is selected with MOD0 high.

The low-pass frequency and the impulse response of the half-

and the idealized filter coefficients are listed in Table 5. Note

that the impulse response of a FIR filter is also represented by

its idealized filter coefficients.

The 2× interpolation filter essentially multiplies the input data rate

to the DAC by a factor of 2, relative to its original input data rate,

while reducing the magnitude of the first image associated with

the original input data rate occurring at fDATA fFUNDAMENTAL. As a

result of the 2× interpolation, the digital filter frequency response is

uniquely defined over its Nyquist zone of dc to fDATA, with mirror

images occurring in adjacent Nyquist zones.

The benefits of an interpolation filter are clearly seen in

Figure 27, which shows an example of the frequency and time

domain representation of a discrete time sine wave signal before

and after it is applied to the 2× digital interpolation filter in a

low-pass configuration. Images of the sine wave signal appear

around multiples of the input data rate (that is, fDATA) of the DAC,

as predicted by sampling theory. These undesirable images also

appear at the output of a reconstruction DAC, although they are

attenuated by the sin(x)/x roll-off response of the DAC.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ECE-V1VA101UP | CAP ALUM 100UF 35V 20% SMD |

| 94SVP107X0016F8 | CAP ALUM 100UF 16V 20% SMD |

| MAX8586ETA+T | IC USB SWITCH 1.2A 8-TDFN |

| AD9764-EBZ | BOARD EVAL FOR AD9764 |

| HCM11DSEH-S243 | CONN EDGECARD 22POS .156 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9772AST | 制造商:Rochester Electronics LLC 功能描述:14 BIT DAC W/2X INTERPOLA - Tape and Reel |

| AD9772EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 160 MSPS TxDAC+ with 2x Interpolation Filter |

| AD9773 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Analog Devices: Data Converters: DAC 12-Bit, 10 ns to 100 ns Converters Selection Table |

| AD9773AST | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 160 MSPS 2】/4】/8】 Interpolating Dual TxDAC+ D/A Converter |

| AD9773BSV | 制造商:Analog Devices 功能描述:DAC 2-CH R-2R 12-bit 80-Pin TQFP EP 制造商:Rochester Electronics LLC 功能描述:12BIT 160 MSPS DUAL TXDAC+ D/A CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC 12-BIT DAC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。