- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19380 > ADSP-2183KCAZ-210 (Analog Devices Inc)IC DSP 16BIT 52MHZ 144-BGA PDF資料下載

參數(shù)資料

| 型號: | ADSP-2183KCAZ-210 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 26/31頁 |

| 文件大小: | 0K |

| 描述: | IC DSP 16BIT 52MHZ 144-BGA |

| 標準包裝: | 1 |

| 系列: | ADSP-21xx |

| 類型: | 定點 |

| 接口: | 同步串行端口(SSP) |

| 時鐘速率: | 52MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 80kB |

| 電壓 - 輸入/輸出: | 3.30V |

| 電壓 - 核心: | 3.30V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LFBGA |

| 供應(yīng)商設(shè)備封裝: | 144-迷你型BGA |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁

ADSP-2183

–4–

REV. C

SPORTs support serial data word lengths from 3 to 16 bits

and provide optional A-law and

-law companding according

to CCITT recommendation G.711.

SPORT receive and transmit sections can generate unique

interrupts on completing a data word transfer.

SPORTs can receive and transmit an entire circular buffer of

data with only one overhead cycle per data word. An interrupt

is generated after a data buffer transfer.

SPORT0 has a multichannel interface to selectively receive

and transmit a 24 or 32 word, time-division multiplexed,

serial bitstream.

SPORT1 can be configured to have two external interrupts

(

IRQ0 and IRQ1) and the Flag In and Flag Out signals. The

internally generated serial clock may still be used in this

configuration.

Pin Descriptions

The ADSP-2183 is available in a 128-lead LQFP package, and

Mini-BGA.

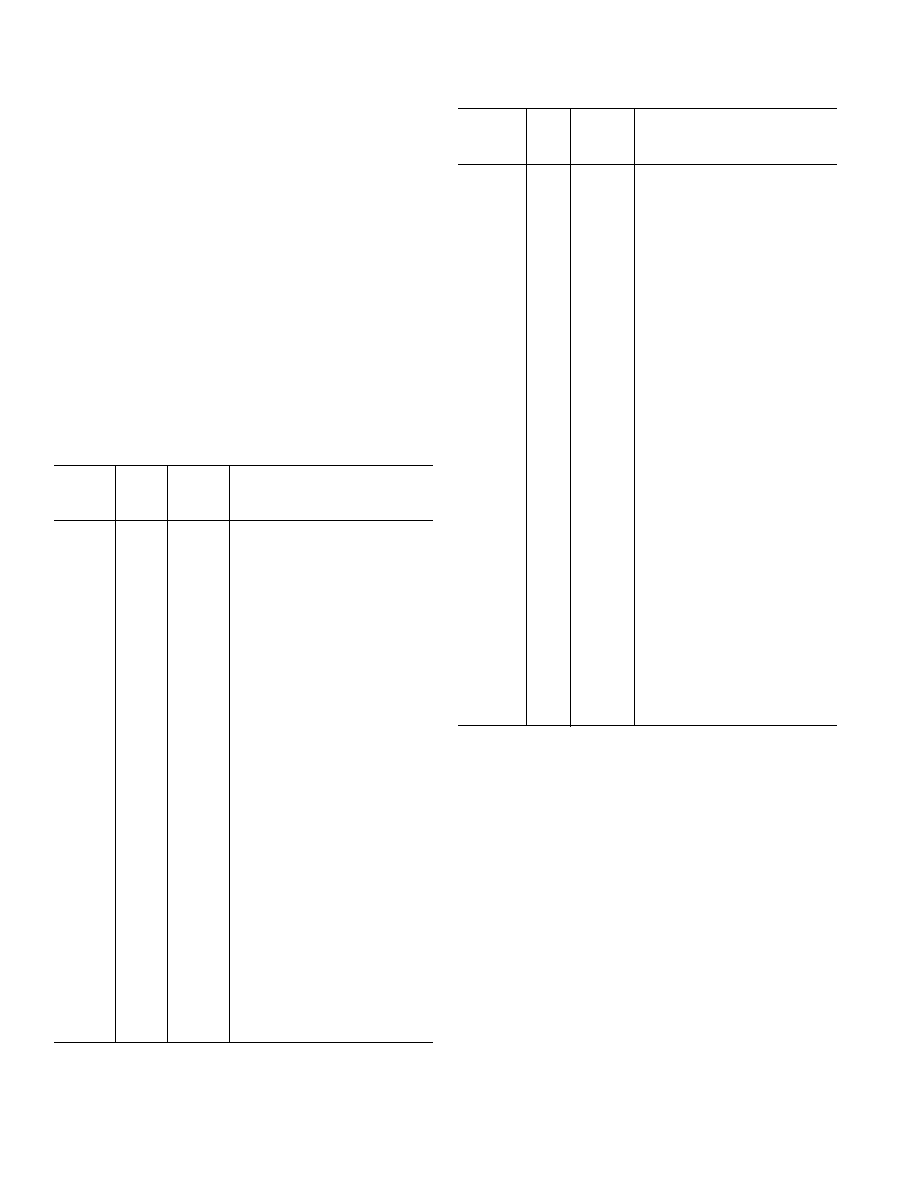

PIN FUNCTION DESCRIPTIONS

#

Pin

of

Input/

Name(s)

Pins

Output Function

Address

14

O

Address Output Pins for Program,

Data, Byte, & I/O Spaces

Data

24

I/O

Data I/O Pins for Program and

Data Memory Spaces (8 MSBs

Are Also Used as Byte Space

Addresses)

RESET

1

I

Processor Reset Input

IRQ2

1

I

Edge- or Level-Sensitive

Interrupt Request

IRQL0,

IRQL1

2

I

Level-Sensitive Interrupt

Requests

IRQE

1

I

Edge-Sensitive Interrupt

Request

BR

1

I

Bus Request Input

BG

1

O

Bus Grant Output

BGH

1

O

Bus Grant Hung Output

PMS

1

O

Program Memory Select Output

DMS

1

O

Data Memory Select Output

BMS

1

O

Byte Memory Select Output

IOMS

1

O

I/O Space Memory Select Output

CMS

1

O

Combined Memory Select Output

RD

1

O

Memory Read Enable Output

WR

1

O

Memory Write Enable Output

MMAP

1

I

Memory Map Select Input

BMODE

1

I

Boot Option Control Input

CLKIN,

XTAL

2

I

Clock or Quartz Crystal Input

#

Pin

of

Input/

Name(s)

Pins

Output Function

CLKOUT

1

O

Processor Clock Output.

SPORT0

5

I/O

Serial Port I/O Pins

SPORT1

5

I/O

Serial Port 1 or Two External

IRQs, Flag In and Flag Out

IRD, IWR 2

I

IDMA Port Read/Write Inputs

IS

1

I

IDMA Port Select

IAL

1

I

IDMA Port Address Latch

Enable

IAD

16

I/O

IDMA Port Address/Data Bus

IACK

1

O

IDMA Port Access Ready

Acknowledge

PWD

1

I

Power-Down Control

PWDACK 1

O

Power-Down Control

FL0, FL1,

FL2

3

O

Output Flags

PF7:0

8

I/O

Programmable I/O Pins

EE

1

*

(Emulator Only*)

EBR

1

*

(Emulator Only*)

EBG

1

*

(Emulator Only*)

ERESET

1

*

(Emulator Only*)

EMS

1

*

(Emulator Only*)

EINT

1

*

(Emulator Only*)

ECLK

1

*

(Emulator Only*)

ELIN

1

*

(Emulator Only*)

ELOUT

1

*

(Emulator Only*)

GND

11

Ground Pins (LQFP)

VDD

6

Power Supply Pins (LQFP)

GND

22

Ground Pins (Mini-BGA)

VDD

11

Power Supply Pins (Mini-BGA)

*These ADSP-2183 pins must be connected only to the EZ-ICE connector in

the target system. These pins have no function except during emulation, and

do not require pull-up or pull-down resistors.

Interrupts

The interrupt controller allows the processor to respond to the

eleven possible interrupts and reset with minimum overhead.

The ADSP-2183 provides four dedicated external interrupt

input pins,

IRQ2, IRQL0, IRQL1 and IRQE. In addition,

SPORT1 may be reconfigured for

IRQ0, IRQ1, FLAG_IN and

FLAG_OUT, for a total of six external interrupts. The ADSP-

2183 also supports internal interrupts from the timer, the byte

DMA port, the two serial ports, software and the power-down

control circuit. The interrupt levels are internally prioritized and

individually maskable (except power-down and reset). The

IRQ2, IRQ0 and IRQ1 input pins can be programmed to be

either level- or edge-sensitive.

IRQL0 and IRQL1 are level-

sensitive and

IRQE is edge sensitive. The priorities and vector

addresses of all interrupts are shown in Table I.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX6670AUB50+T | IC TEMP SENSOR REMOTE 10-UMAX |

| MC7824CT | IC REG LDO 24V 1A TO220AB |

| GBC07DRTS | CONN EDGECARD 14POS DIP .100 SLD |

| ABE35DHRR | CONN CARD EXTEND 70POS 1MM SLD |

| RSC35DRSD-S273 | CONN EDGECARD 70POS DIP .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP2183KS133 | 制造商:AD 功能描述:* |

| ADSP-2183KST-115 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2183KST-133 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 33.3MHz 33.3MIPS 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:3.3V 16BITDSP,33MIPS,16KWRDSPM/DM,128TQF - Bulk |

| ADSP-2183KST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 40MHz 40MIPS 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:3.3V,16BITDSP,40MIPS,16KWRDSPM/DM,128TQF - Bulk |

| ADSP-2183KST-210 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 52MHz 52MIPS 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:3.3V 16BITDSP,52MIPS,16KWORDSPM/DM,128TQ - Bulk 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。