- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C972BVIW (ADVANCED MICRO DEVICES INC) PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C972BVIW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| 中文描述: | 5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP176 |

| 封裝: | TQFP-176 |

| 文件頁(yè)數(shù): | 87/130頁(yè) |

| 文件大小: | 1580K |

| 代理商: | AM79C972BVIW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)當(dāng)前第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)

Am79C972

87

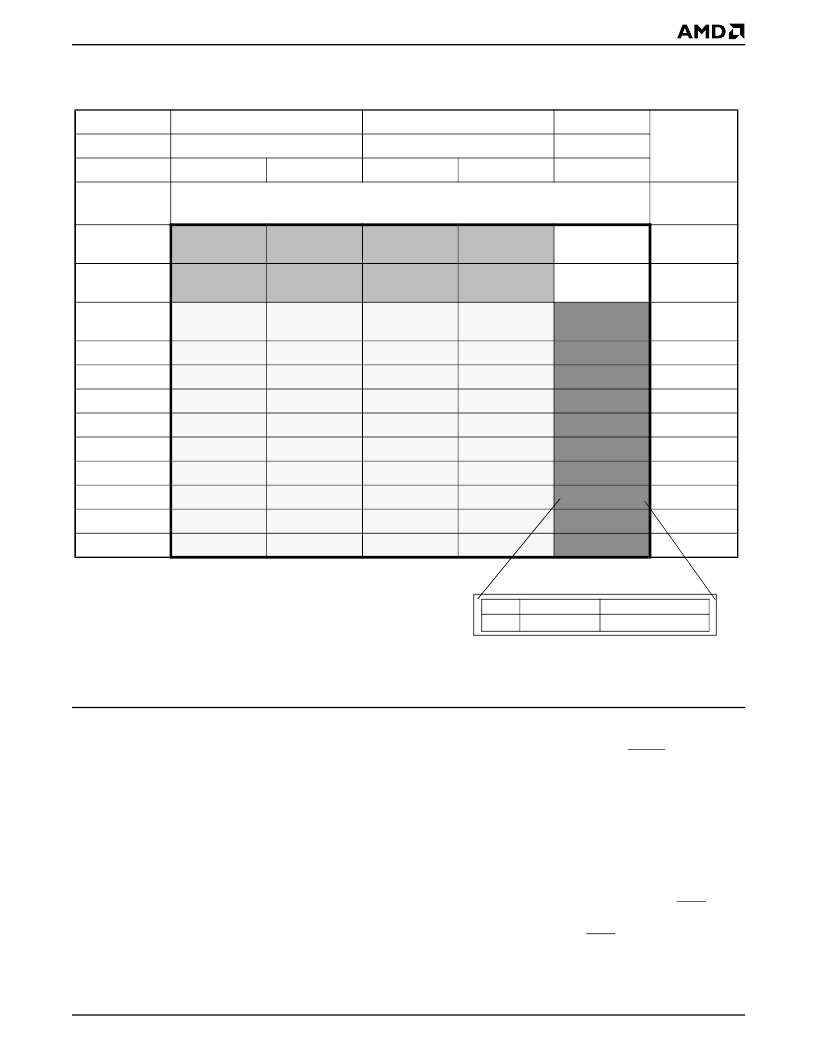

Figure 49.

Pattern Match RAM

There are two general methods to place the PCnet-

FAST

+ into the Magic Packet mode. The first is the soft-

ware method. In this method, either the BIOS or other

software, sets the MPMODE bit (CSR5, bit 1). Then

PCnet-

FAST

+ controller must be put into suspend

mode (see description of CSR5, bit 0), allowing any

current network activity to finish. Finally, either PG must

be deasserted (hardware control) or MPEN (CSR5, bit

2) must be set to 1 (software control).

Note:

FASTSPNDE (CSR7, bit 15) has no meaning in

Magic Packet mode.

The second method is the hardware method. In this

method, the MPPEN bit (CSR116, bit 4) is set at power

up by the loading of the EEPROM. This bit can also be

set by software. The PCnet-

FAST

+ will be placed in the

Magic Packet Mode when either the PG input is

deasserted or the MPEN bit is set. WUMI output will be

asserted when the PCnet-

FAST

+ is in the Magic

Packet mode. Magic Packet mode can be disabled at

any time by asserting PG or clearing MPEN bit.

When the PCnet-

FAST

+ controller detects a Magic

Packet frame, it sets the MPMAT bit (CSR116, bit 5),

the MPINT bit (CSR5, bit 4), and the PME_STATUS bit

(PMCSR, bit 15). The setting of the MPMAT bit will also

cause the RWU pin to be asserted and if the PME_EN

or the PME_EN_OVR bits are set, then the PME will be

asserted as well. If IENA (CSR0, bit 6) and MPINTE

(CSR5, bit 3) are set to 1, INTA will be asserted. Any

one of the four LED pins can be programmed to indi-

cate that a Magic Packet frame has been received.

BCR 47

BCR 46

BCR 45

BCR Bit Number 15 8 7 0 15 8 7 0 15 8

PMR_B4

PMR_B3

PMR_B2

PMR_B1

PMR_B0

Pattern Match

RAM Address

Pattern Match RAM Bit Number

39 32 31 24 23 16 15 8 7 0

Comments

0

P3 pointer

P2 pointer

P1 pointer

P0 pointer

Pattern Enable

bits

First Address

1

P7 pointer

P6 pointer

P5 pointer

P4 pointer

X

Second

Address

2

Data Byte 3

Data Byte 2

Data Byte1

Data Byte 0

Pattern Control

Start Pattern

P

1

2+n

Data Byte 4n+3

Date Byte 4n+2

Data Byte 4n+1

Data Byte 4n+0

Pattern Control

End Pattern P

1

J

Data Byte 3

Data Byte 2

Data Byte 1

Data Byte 0

Pattern Control

Start Pattern P

k

J+m

Data Byte 4m+3 Data Byte 4m+2 Data Byte 4m+1 Data Byte 4m+0

Pattern Control

End Pattern P

k

63

Last Address

7 6 5 4 3 2 1 0

EOP SKIP MASK

21485C-52

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C974 | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C973 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973/75 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Board Layout Considerations for the Am79C973/75 Network Interface? - (PDF) |

| AM79C973/AM79C975 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Am79C973/Am79C975 - PCnet-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973AVC\\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C973AVC\W | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。