- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4476 > APA075-PQG208I (Microsemi SoC)IC FPGA PROASIC+ 75K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | APA075-PQG208I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 162/178頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA PROASIC+ 75K 208-PQFP |

| 標準包裝: | 24 |

| 系列: | ProASICPLUS |

| RAM 位總計: | 27648 |

| 輸入/輸出數(shù): | 158 |

| 門數(shù): | 75000 |

| 電源電壓: | 2.3 V ~ 2.7 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁當前第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁

ProASICPLUS Flash Family FPGAs

2- 74

v5.9

VPP

Programming Supply Pin

This pin may be connected to any voltage between GND

and 16.5 V during normal operation, or it can be left

unconnected.2 For information on using this pin during

programming,

see

the

ProASICPLUS Devices application note. Actel recommends

floating the pin or connecting it to VDDP.

VPN

Programming Supply Pin

This pin may be connected to any voltage between 0.5 V

and –13.8 V during normal operation, or it can be left

unconnected.3 For information on using this pin during

programming,

see

the

ProASICPLUS Devices application note. Actel recommends

floating the pin or connecting it to GND.

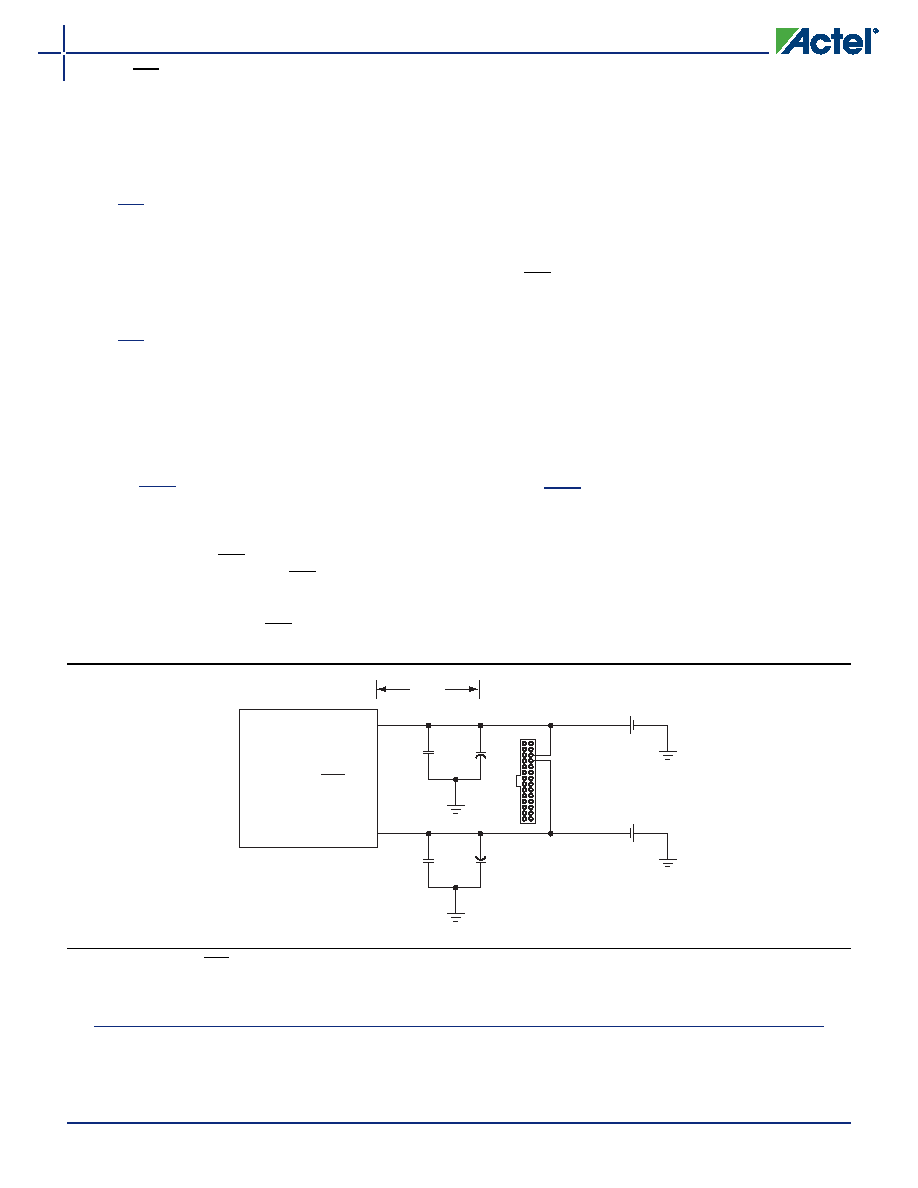

Recommended Design Practice

for VPN/VPP

ProASICPLUS Devices – APA450, APA600,

APA750, APA1000

Bypass capacitors are required from VPP to GND and VPN

to GND for all ProASICPLUS devices during programming.

During the erase cycle, ProASICPLUS devices may have

current surges on the VPP and VPN power supplies. The

only way to maintain the integrity of the power

distribution to the ProASICPLUS device during these

current surges is to counteract the inductance of the

finite length conductors that distribute the power to the

device. This can be accomplished by providing sufficient

bypass capacitance between the VPP and VPN pins and

GND (using the shortest paths possible). Without

sufficient

bypass

capacitance

to

counteract

the

inductance, the VPP and VPN pins may incur a voltage

spike beyond the voltage that the device can withstand.

This issue applies to all programming configurations.

The solution prevents spikes from damaging the

ProASICPLUS devices. Bypass capacitors are required for

the VPP and VPN pads. Use a 0.01 F to 0.1 F ceramic

capacitor with a 25 V or greater rating. To filter low-

frequency noise (decoupling), use a 4.7 F (low ESR, <1

<

Ω, tantalum, 25 V or greater rating) capacitor. The

capacitors should be located as close to the device pins as

possible (within 2.5 cm is desirable). The smaller, high-

frequency capacitor should be placed closer to the device

pins than the larger low-frequency capacitor. The same

dual-capacitor circuit should be used on both the VPP and

ProASICPLUS Devices – APA075, APA150,

APA300

These devices do not require bypass capacitors on the VPP

and VPN pins as long as the total combined distance of

the programming cable and the trace length on the

board is less than or equal to 30 inches. Note: For trace

lengths greater than 30 inches, use the bypass capacitor

recommendations in the previous section.

2. There is a nominal 40 k

Ω pull-up resistor on V

PP.

3. There is a nominal 40 k

Ω pull-down resistor on V

PN.

Figure 2-46 ProASICPLUS VPP and VPN Capacitor Requirements

2.5cm

0.1 F

to

0.01 F

Programming

Header

or

Supplies

4.7 F

Actel

ProASIC

Device

+

_

V

PP

V

PN

+

_

0.1 F

to

0.01 F

4.7 F

PLUS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSA50DRSI-S288 | CONN EDGECARD 100PS .125 EXTEND |

| APA075-PQ208I | IC FPGA PROASIC+ 75K 208-PQFP |

| A40MX04-3VQ80 | IC FPGA MX SGL CHIP 6K 80-VQFP |

| IDT71V3578S133PFG | IC SRAM 4MBIT 133MHZ 100TQFP |

| A40MX04-3VQG80 | IC FPGA MX SGL CHIP 6K 80-VQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| APA075-PQGB | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA075-PQGES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA075-PQGI | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA075-PQGM | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA075-PQGPP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。