- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄295111 > AT17LV040-10BJC (ATMEL CORP) FPGA Configuration EEPROM Memory PDF資料下載

參數(shù)資料

| 型號(hào): | AT17LV040-10BJC |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | PROM |

| 英文描述: | FPGA Configuration EEPROM Memory |

| 中文描述: | 4M X 1 CONFIGURATION MEMORY, PQCC44 |

| 封裝: | PLASTIC, MS-018AC, LCC-44 |

| 文件頁(yè)數(shù): | 27/29頁(yè) |

| 文件大?。?/td> | 412K |

| 代理商: | AT17LV040-10BJC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)

7

2321H–CNFG–03/06

AT17LV65/128/256/512/010/002/040

3.

Device Description

The control signals for the configuration EEPROM (CE, RESET/OE and CCLK) interface directly

with the FPGA device control signals. All FPGA devices can control the entire configuration pro-

cess and retrieve data from the configuration EEPROM without requiring an external intelligent

controller.

The configuration EEPROM RESET/OE and CE pins control the tri-state buffer on the DATA

output pin and enable the address counter. When RESET/OE is driven High, the configuration

EEPROM resets its address counter and tri-states its DATA pin. The CE pin also controls the

output of the AT17LV series configurator. If CE is held High after the RESET/OE reset pulse, the

counter is disabled and the DATA output pin is tri-stated. When OE is subsequently driven Low,

the counter and the DATA output pin are enabled. When RESET/OE is driven High again, the

address counter is reset and the DATA output pin is tri-stated, regardless of the state of CE.

When the configurator has driven out all of its data and CEO is driven Low, the device tri-states

the DATA pin to avoid contention with other configurators. Upon power-up, the address counter

is automatically reset.

This is the default setting for the device. Since almost all FPGAs use RESET Low and OE High,

this document will describe RESET/OE.

Note:

1. The CEO feature is not available on the AT17LV65 device.

4.

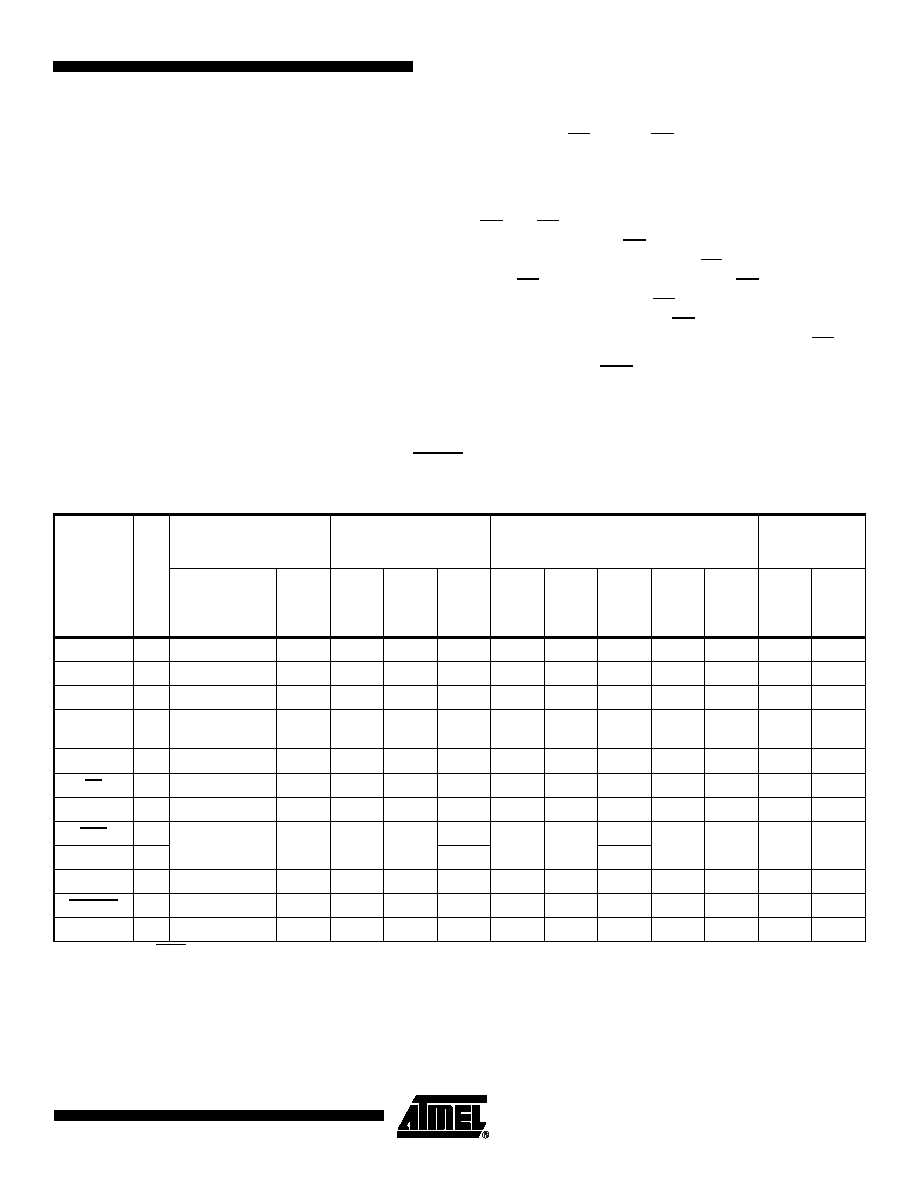

Pin Description

Name

I/O

AT17LV65/

AT17LV128/

AT17LV256

AT17LV512/

AT17LV010

AT17LV002

AT17LV040

8

DIP/

LAP/

SOIC

20

PLCC

20

SOIC

8

DIP/

LAP

20

PLCC

20

SOIC

8

DIP/

LAP/

SOIC

20

PLCC

20

SOIC

44

PLCC

44

TQFP

44

PLCC

44

TQFP

DATA

I/O

12

212

112

12

40

2

40

CLK

I

24

424

324

35

43

5

43

WP1

I

––

––5

–––

––

RESET/

O

E

I

3

6

636

836

8

19

13

19

13

WP2

I

–7

––7

–––

––

CE

I

4

8

4

8

10

4

8

10

21

15

21

15

GND

5

10

10510

11510

11

24

18

24

18

CEO

O

614

14614

13

614

13

27

21

27

21

A2

I

–

READY

O

––

15

––

15

–

29

23

29

23

SER_EN

I

7

17

17717

18717

18

41

35

41

35

V

CC

820

20820

20

44

38

44

38

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT17LV128-10BJC | FPGA Configuration EEPROM Memory |

| AT17LV256-10BJC | PhotoMOS Relay; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Voltage:5V RoHS Compliant: No |

| AT17LV512-10BJC | FPGA Configuration EEPROM Memory |

| AT17LV65A-10BJC | FPGA Configuration EEPROM Memory |

| AT24C08SC-09BT | 1K X 8 I2C/2-WIRE SERIAL EEPROM, XMA8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT17LV040-10BJI | 功能描述:FPGA-配置存儲(chǔ)器 Serial EEPROM RoHS:否 制造商:Altera Corporation 存儲(chǔ)類(lèi)型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| AT17LV040-10CC | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV040-10CI | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV040-10JC | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV040-10JI | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。