- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67388 > AT30TS750-MA8-T (ATMEL CORP) DIGITAL TEMP SENSOR-SERIAL, 12BIT(s), 3Cel, RECTANGULAR, SURFACE MOUNT PDF資料下載

參數(shù)資料

| 型號: | AT30TS750-MA8-T |

| 廠商: | ATMEL CORP |

| 元件分類: | 溫度/濕度傳感器 |

| 英文描述: | DIGITAL TEMP SENSOR-SERIAL, 12BIT(s), 3Cel, RECTANGULAR, SURFACE MOUNT |

| 封裝: | 2 X 3 MM, 0.60 MM HEIGHT, GREEN, PLASTIC, MO-229, UDFN-8 |

| 文件頁數(shù): | 21/52頁 |

| 文件大小: | 1369K |

| 代理商: | AT30TS750-MA8-T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

R

will be recognized by the device with the remaining LSBs being internally fixed to the logic “0”

state. Similarly, when reading from the registers, up to 12 bits of data will be output from the

device with the remaining LSBs fixed in the logic “0” state.

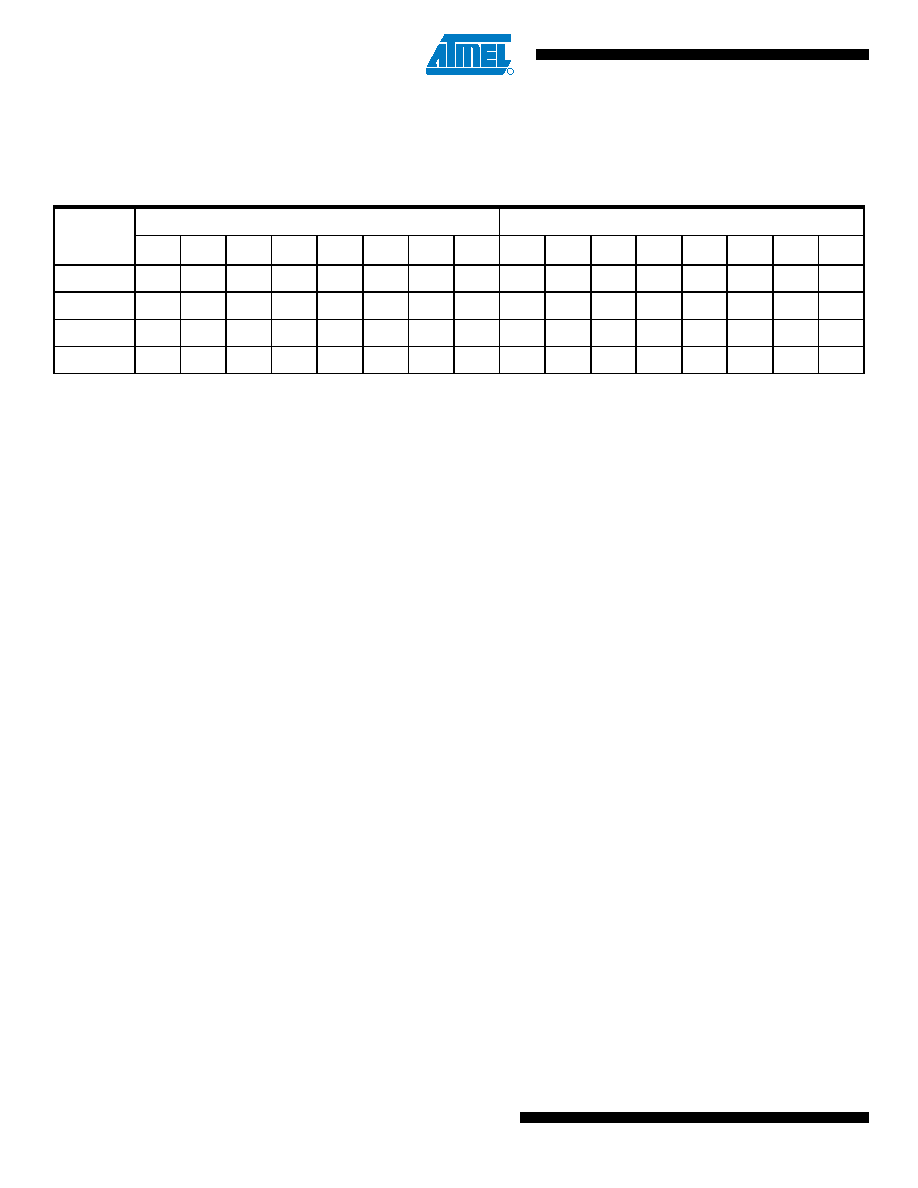

Table 6-11.

TLOW Limit Register and THIGH Limit Register Format

Upper Byte

Lower Byte

Resolution

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

12 bits

Sign

TD

0

11 bits

Sign

TD

0

10 bits

Sign

TD

0

9 bits

Sign

TD

0

Note:

TD = Temperature Data

To set the value of either the TLOW or THIGH Limit Register, the Master must first initiate a

START condition followed by the AT30TS750’s device address byte (1001AAA0 where “AAA”

corresponds to the hard-wired A2-0 address pins). After the AT30TS750 has received the proper

address byte, the device will send an ACK to the Master.

The Master must then send the

appropriate Pointer Register byte of 02h to select the TLOW Limit Register or 03h to select the

THIGH Limit Register. After the Pointer Register byte has been sent, the AT30TS750 will send

another ACK to the Master. After receiving the ACK from the AT30TS750, the Master must then

send two data bytes to the AT30TS750 to set the value of the TLOW or THIGH Limit Register. Any

subsequent bytes sent to the AT30TS750 will simply be ignored by the device. If the Master does

not send two complete bytes of data prior to issuing a STOP or repeated START condition, then

the AT30TS750 will ignore the data and the contents of the register will not be changed.

In addition to the Master not sending two complete bytes of data, writing to the TLOW or THIGH

Limit Register will be ignored and no operation will be performed under the following conditions:

the nonvolatile registers are busy because of a copy operation (the NVRBSY bit of the

Configuration Register is in the logic “1” state), the volatile and nonvolatile registers are currently

locked (the RLCK bit of the Nonvolatile Configuration Register is in the logic “1” state), or the

volatile and nonvolatile registers are permanently locked down (the RLCKDWN bit of the

Nonvolatile Configuration Register is in the logic “1” state). However, the device will still respond

with an ACK, except in the case of the nonvolatile registers being busy, to indicate that it received

the proper data bytes even though the contents of the TLOW or THIGH Limit Register will not be

changed. In the case of the nonvolatile registers being busy, the device will respond with an ACK

to the address and pointer bytes but will then NACK when the data bytes are sent from the

Master.

In order to read the TLOW or THIGH Limit Register, the Pointer Register must be set or have been

previously set to 02h to select the TLOW Limit Register or 03h to select the THIGH Limit Register

(if the previous operation was a write to one of the registers, then the Pointer Register will already

be set for that particular limit register). If the Pointer Register has already been set appropriately,

the TLOW or THIGH Limit Register can be read by having the Master first initiate a START

condition followed by the AT30TS750’s device address byte (1001AAA1 where “AAA”

corresponds to the hard-wired A2-0 address pins). After the AT30TS750 has received the proper

address byte, the device will send an ACK to the Master. The Master can then read the upper

byte of the TLOW or THIGH Limit Register. After the upper byte of the register has been clocked

8749A-DTS-03/11

Atmel AT30TS750 [Preliminary]

28

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT30TS750-XM8-B | DIGITAL TEMP SENSOR-SERIAL, 12BIT(s), 3Cel, SQUARE, SURFACE MOUNT |

| AT42QT1070-SSU | PROXIMITY SENSOR-CAPACITIVE, 0.6-2.6V, RECTANGULAR, SURFACE MOUNT |

| AT42QT1110-AZ | PROXIMITY SENSOR-CAPACITIVE, 0-5V, SQUARE, SURFACE MOUNT |

| AT42QT1110-MZ | PROXIMITY SENSOR-CAPACITIVE, 0-5V, SQUARE, SURFACE MOUNT |

| AT42QT1111-AU | PROXIMITY SENSOR-CAPACITIVE, 0-5V, SQUARE, SURFACE MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT30TS750SS8B | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:9- to 12-bit Selectable, ?±0.5?°C Accurate Digital Temperature Sensor with Nonvolatile Registers |

| AT30TS750-SS8-B | 功能描述:板上安裝溫度傳感器 TMP SENSOR RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關(guān)閉: 安裝風(fēng)格: 封裝 / 箱體: 設(shè)備功能:Temperature and Humidity Sensor |

| AT30TS750SS8T | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:9- to 12-bit Selectable, ?±0.5?°C Accurate Digital Temperature Sensor with Nonvolatile Registers |

| AT30TS750-SS8-T | 功能描述:板上安裝溫度傳感器 TMP SENSOR RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關(guān)閉: 安裝風(fēng)格: 封裝 / 箱體: 設(shè)備功能:Temperature and Humidity Sensor |

| AT30TS750XM8B | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:9- to 12-bit Selectable, ?±0.5?°C Accurate Digital Temperature Sensor with Nonvolatile Registers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。