- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄223464 > BU-61845G4-132K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-61845G4-132K |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| 封裝: | GULL WING, PACKAGE-72 |

| 文件頁(yè)數(shù): | 32/56頁(yè) |

| 文件大?。?/td> | 321K |

| 代理商: | BU-61845G4-132K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

38

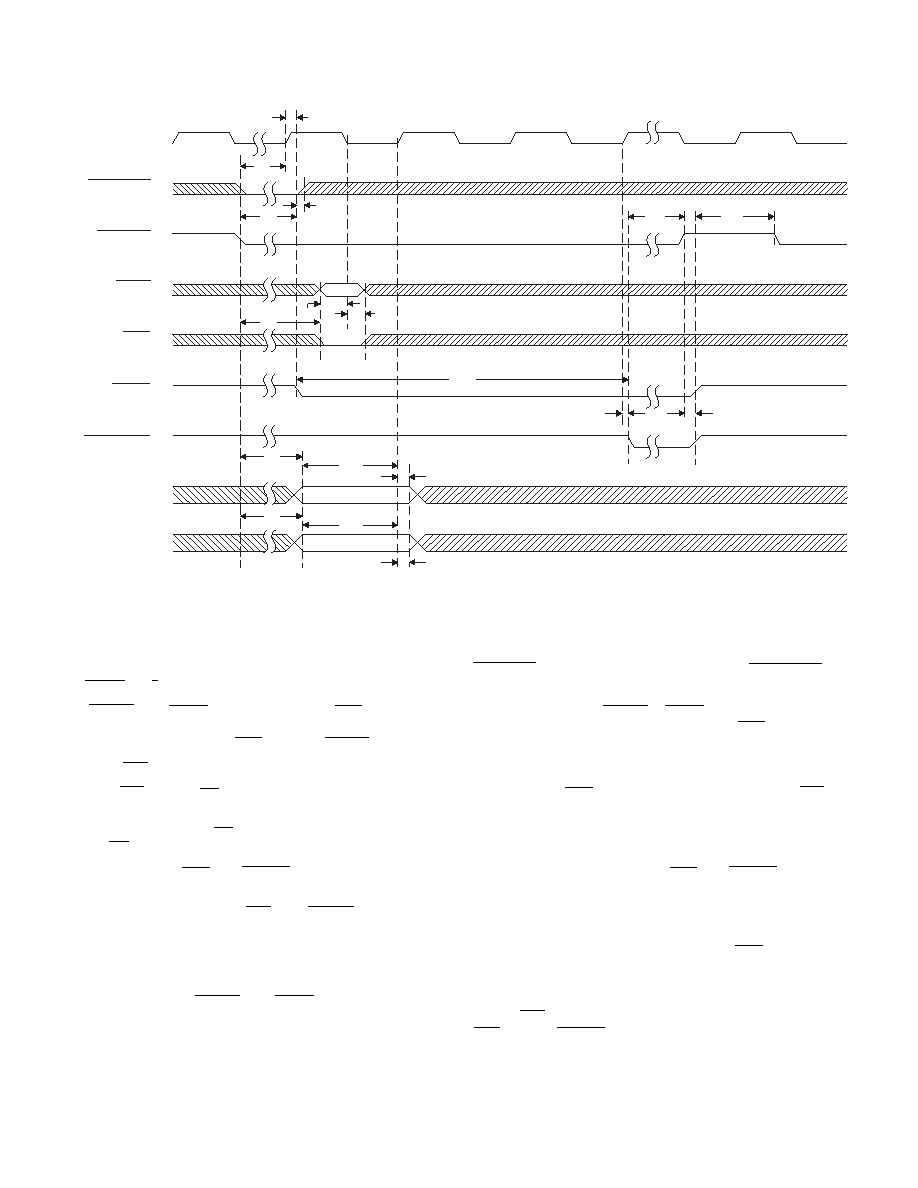

CLOCK IN

t1

t6

t7

t2

t3

t18

t16

VALID

t8

t9

t14

t15

t17

VALID

t12

t10

t4

t11

t5

VALID

t13

SELECT

(Note 2,7)

(Note 2)

(Note 3,4,7)

(Note 4,5)

STRBD

MEM/REG

RD/WR

IOEN

(Note 2,6)

(Note 6)

(Note 9,10)

(Note 7,8,9,10)

READYD

A15-A0

D15-D0

FIGURE 14. CPU WRITING RAM / REGISTER (16-BIT BUFFERED, NONZERO WAIT)

NOTES:

1.

For the 16-bit buffered nonzero wait configuration

must be connected to logic "0",

and

must be connected to logic "1". The inputs TRIGGER_SEL and MSB/LSB may be connected to either +5V or ground.

2.

and

may be tied together.

goes low on the first rising CLK edge when

is sampled low (satisfying

t1) and the Enhanced Mini-ACE's protocol/memory management logic is not accessing the internal RAM. When this occurs,

goes low, start-

ing the transfer cycle. After

goes low,

may be released high.

3.

must be presented high for memory access, low for register access.

4.

and

are buffered transparently until the first falling edge of CLK after

goes low. After this CLK edge,

and

become latched internally.

5.

The logic sense for

in the diagram assumes that POLARITY_SEL is connected to logic "1." If POLARITY_SEL is connected to logic "0,"

must be asserted high to write.

6.

The timing for the

and

outputs assumes a 50 pf load. For loading above 50 pf, the validity of

and

is delayed by

an additional 0.14 ns/pf typ, 0.28 ns/pf max.

7.

The timing for A15-A0,

, and

assumes that ADDR-LAT is connected to logic "1." Refer to Address Latch timing for addi-

tional details.

9.

The address bus A15-A0 and data bus D15-D0 are internally buffered transparently until the first rising edge of CLK after

goes low. After

this CLK edge, A15-A0 and D15-D0 become latched internally.

10. Setup time given for use in worst case timing calculations. None of the Enhanced Mini-ACE input signals are required to be synchronized to the

system clock. When

and

do not meet the setup time of t1, but occur during the setup time of an internal flip-flop, an addition-

al clock cycle may be inserted between the falling clock edge that latches

and

and the rising clock edge that latches the

address (A15-A0) and data (D15-D0). When this occurs, the delay from

falling to

falling (t14) increases by one clock cycle and

the address and data hold time (t12 and t13) must be increased by one clock.

READYD

IOEN

WR

/

RD

REG

/

MEM

STRBD

SELECT

IOEN

SELECT

REG

/

MEM

READYD

IOEN

READYD

IOEN

WR

/

RD

WR

/

RD

WR

/

RD

REG

/

MEM

IOEN

WR

/

RD

REG

/

MEM

REG

/

MEM

SELECT

IOEN

STRBD

SELECT

IOEN

STRBD

SELECT

8

/

16

/

DTREQ

WAIT

ZERO

BUFFERED

/

T

TRANSPAREN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61845G4-192S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61864G4-122Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61865F4-192 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865G4-162K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61745G4 | 2 CHANNEL(S), MIL-STD-1553 CONTROLLER, CQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61860B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61864 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61864F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864F4-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。