- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄210366 > BX80532KC1900E (INTEL CORP) 1900 MHz, MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | BX80532KC1900E |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1900 MHz, MICROPROCESSOR |

| 文件頁(yè)數(shù): | 30/132頁(yè) |

| 文件大小: | 2316K |

| 代理商: | BX80532KC1900E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)

Intel Xeon Processor MP with up to 2MB L3 Cache

9-27

NOTES:

1. Intel Xeon processors only support BR0# and BR1#. However, the Intel Xeon processors must terminate

BR2# and BR3# to the processor VCC..

§

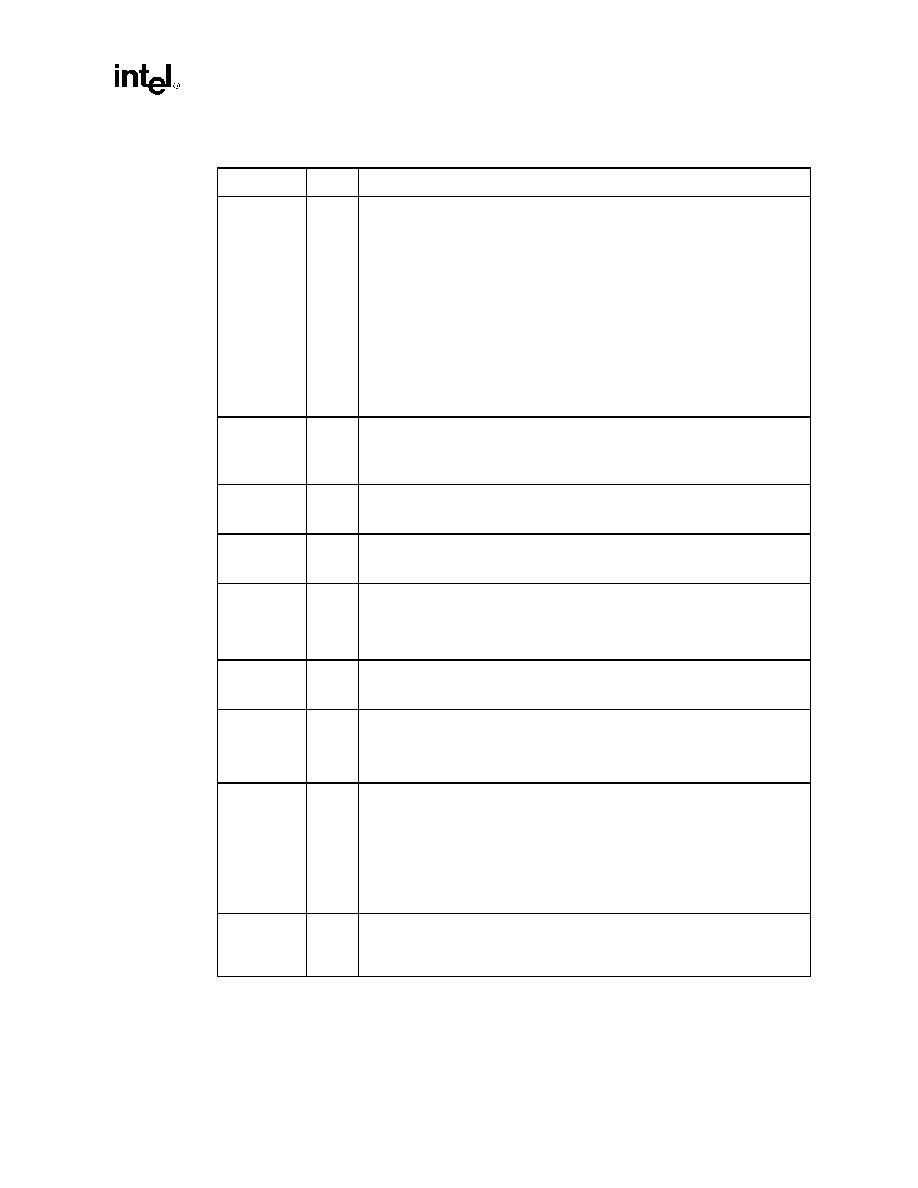

THERMTRIP#

O

Assertion of THERMTRIP# (Thermal Trip) indicates the processor junction

temperature has reached a level where permanent silicon damage may occur.

Measurement of the temperature is accomplished through an internal thermal

sensor which is configured to trip at approximately 135°C. Upon assertion of

THERMTRIP#, the processor will shut off its internal clocks (thus halting program

execution) in an attempt to reduce the processor junction temperature. To protect

the processor, its core voltage (Vcc) must be removed following the assertion of

sequence and timing requirements.

Once activated, THERMTRIP# remains latched until RESET# is asserted. While

the assertion of the RESET# signal will de-assert THERMTRIP#, if the processor’s

junction temperature remains at or above the trip level, THERMTRIP# will again be

asserted.

This signal does not have on-die termination and must be terminated at the end

agent. See the appropriate platform design guideline for additional information.

TMS

I

TMS (Test Mode Select) is a JTAG specification support signal used by debug

tools.

This signal does not have on-die termination and must be terminated at the end

agent. See the appropriate platform design guideline for additional information.

TRDY#

I

TRDY# (Target Ready) is asserted by the target to indicate that it is ready to receive

a write or implicit writeback data transfer. TRDY# must connect the appropriate pins

of all system bus agents.

TRST#

I

TRST# (Test Reset) resets the Test Access Port (TAP) logic. TRST# must be driven

low during power on Reset. See the appropriate platform design guideline for

additional information.

VCCA

I

VCCA provides isolated power for the analog portion of the internal PLL’s. Use a

discrete RLC filter to provide clean power. Use the filter defined in Section 2.5 to

provide clean power to the PLL. The tolerance and total ESR for the filter is

important. Refer to the appropriate platform design guidelines for complete

implementation details.

VCCIOPLL

I

VCCIOPLL provides isolated power for digital portion of the internal PLL’s. Follow the

guidelines for VCCA (Section 2.5). Refer to the appropriate platform design

guidelines for complete implementation details.

VCCSENSE

VSSSENSE

O

The Vccsense and Vsssense pins are the points for which processor minimum and

maximum voltage requirements are specified. Uniprocessor designs may utilize

these pins for voltage sensing for the processor's voltage regulator. However, multi-

processor designs must not connect these pins to sense logic, but rather utilize

them for power delivery validation

.

VID[4:0]

O

VID[4:0] (Voltage ID) pins can be used to support automatic selection of power

supply voltages (VCC). Unlike previous generations of processors, these are logic

signals and are driven by the Intel Xeon processor MP on the 0.13 micron process

processor. Hence the voltage supply for these pins (SM_Vcc) must be valid before

the VRM supplying Vcc to the processor is enabled (see Figure ). Conversely, the

VRM output must be disabled prior to the voltage supply for these pins becomes

invalid. The VID pins are needed to support processor voltage specification

variations. See Table 4 for definitions of these pins. The power supply must supply

the voltage that is requested by these pins, or disable itself.

VSSA

I

VSSA provides an isolated, internal ground for internal PLL’s. Do not connect

directly to ground. This pin is to be connected to VCCA and VCCIOPLL through a

appropriate platform design guidelines for complete implementation details.

Table 52. Signal Definitions (Sheet 9 of 9)

Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61582D0-290S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D0-300K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D1-391Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D1-410S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D1-431 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BX80532KC2000D | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2GHZ - Boxed Product (Development Kits) |

| BX80532KC2000E | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2GHZ - Boxed Product (Development Kits) |

| BX80532KC2200DU | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2.2GHZ 603-PIN IN - Boxed Product (Development Kits) |

| BX80532KC2400D | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2.4GHZ - Boxed Product (Development Kits) |

| BX80532KC2400DU | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2.4GHZ - Boxed Product (Development Kits) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。