- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄26509 > CS2100P-DZZR (CIRRUS LOGIC INC) PDF資料下載

參數(shù)資料

| 型號(hào): | CS2100P-DZZR |

| 廠商: | CIRRUS LOGIC INC |

| 元件分類: | PLL合成/DDS/VCOs |

| 中文描述: | PHASE LOCKED LOOP, 30 MHz, PDSO10 |

| 封裝: | 3 MM, LEAD FREE, MO-187, MSOP-10 |

| 文件頁數(shù): | 25/25頁 |

| 文件大小: | 223K |

| 代理商: | CS2100P-DZZR |

CS2100-OTP

DS841F2

9

4. ARCHITECTURE OVERVIEW

4.1

Delta-Sigma Fractional-N Frequency Synthesizer

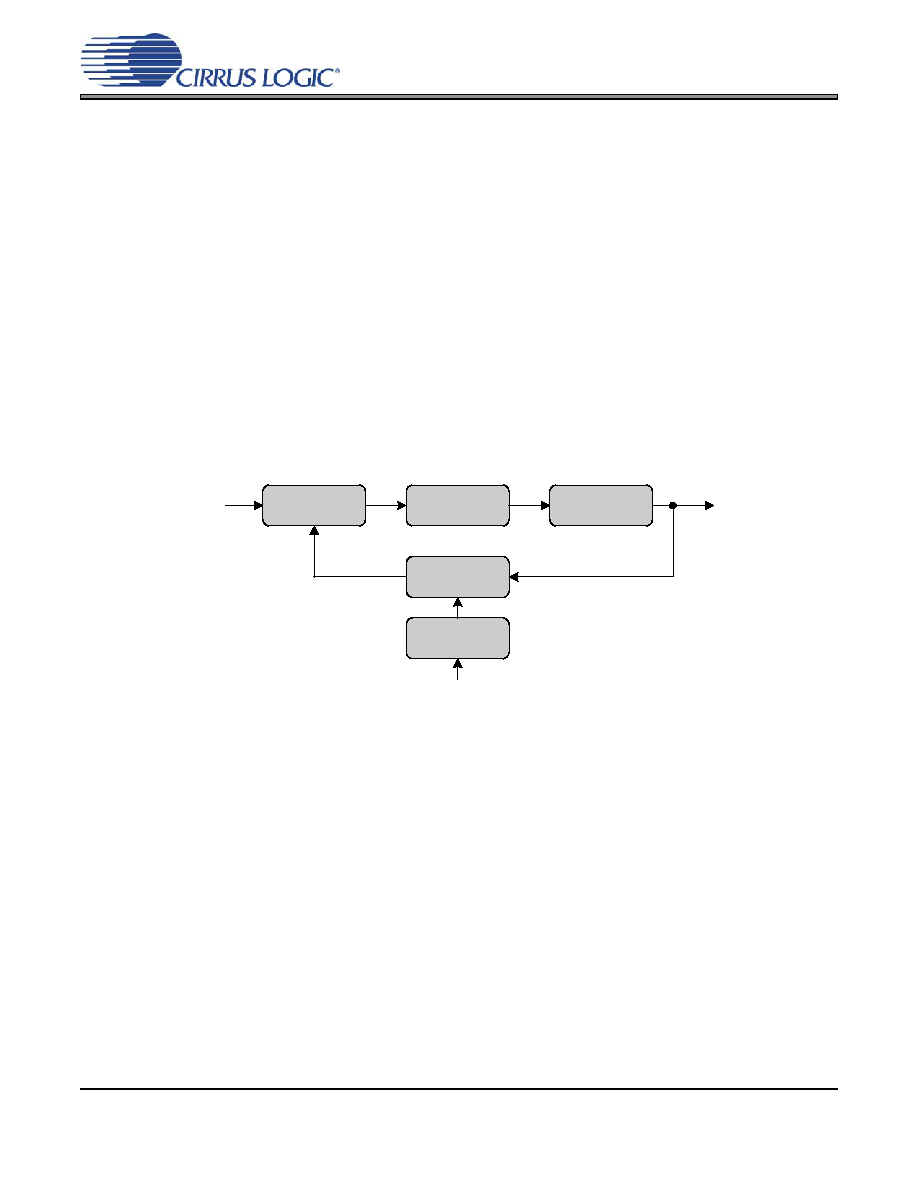

The core of the CS2100 is a Delta-Sigma Fractional-N Frequency Synthesizer which has very high-resolu-

tion for Input/Output clock ratios, low phase noise, very wide range of output frequencies and the ability to

quickly tune to a new frequency. In very simplistic terms, the Fractional-N Frequency Synthesizer multiplies

the Timing Reference Clock by the value of N to generate the PLL output clock. The desired output to input

clock ratio is the value of N that is applied to the delta-sigma modulator (see Figure 5).

The analog PLL based frequency synthesizer uses a low-jitter timing reference clock as a time and phase

reference for the internal voltage controlled oscillator (VCO). The phase comparator compares the fraction-

al-N divided clock with the original timing reference and generates a control signal. The control signal is fil-

tered by the internal loop filter to generate the VCO’s control voltage which sets its output frequency. The

delta-sigma modulator modulates the loop integer divide ratio to get the desired fractional ratio between the

reference clock and the VCO output (thus the duty cycle of the modulator sets the fractional value). This

allows the design to be optimized for very fast lock times for a wide range of output frequencies without the

need for external filter components. As with any Fractional-N Frequency Synthesizer the timing reference

clock should be stable and jitter-free.

Figure 5. Delta-Sigma Fractional-N Frequency Synthesizer

4.2

Hybrid Analog-Digital Phase Locked Loop

The addition of the Digital PLL and Fractional-N Logic (shown in Figure 6) to the Fractional-N Frequency

Synthesizer creates the Hybrid Analog-Digital Phase Locked Loop with many advantages over classical an-

alog PLL techniques. These advantages include the ability to operate over extremely wide frequency ranges

without the need to change external loop filter components while maintaining impressive jitter reduction per-

formance. In the Hybrid architecture, the Digital PLL calculates the ratio of the PLL output clock to the fre-

quency reference and compares that to the desired ratio. The digital logic generates a value of N which is

then applied to the Fractional-N frequency synthesizer to generate the desired PLL output frequency. Notice

that the frequency and phase of the timing reference signal do not affect the output of the PLL since the

digital control loop will correct for the PLL output. A major advantage of the Digital PLL is the ease with which

the loop filter bandwidth can be altered. The PLL bandwidth is set to a wide-bandwidth mode to quickly

achieve lock and then reduced for optimal jitter rejection.

Fractional-N

Divider

Timing Reference

Clock

PLL Output

Voltage Controlled

Oscillator

Internal

Loop Filter

Phase

Comparator

N

Delta-Sigma

Modulator

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CS2200P-DZZR | |

| CS2300P-DZZR | |

| CS3511-CNZR | |

| CS35L00-CNZ | |

| CS4207-DNZR | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS2106 | 制造商:Coilcraft Inc 功能描述:NOT RoHS. Current sense transformer (add 'L' for compliant version) |

| CS2106L | 制造商:Coilcraft Inc 功能描述:Current sense transformer, RoHS |

| CS2113-1 | 制造商:Edwards Signaling & Security Systems 功能描述:BELL 432-115V60HZ OTIS |

| CS2113-10 | 制造商:Edwards Signaling & Security Systems 功能描述:GONG |

| CS2113-2 | 制造商:Edwards Signaling & Security Systems 功能描述:BELL 432 115V60AZ OTIS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。