- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358698 > CY7C43686AV-15AC (CYPRESS SEMICONDUCTOR CORP) 3.3V 1K 4K 16K x 36 x 18 x 2 Tri Bus FIFO PDF資料下載

參數(shù)資料

| 型號: | CY7C43686AV-15AC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | FIFO |

| 英文描述: | 3.3V 1K 4K 16K x 36 x 18 x 2 Tri Bus FIFO |

| 中文描述: | 16K X 36 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 封裝: | 14 X 20 MM, 1.40 MM HEIGHT, PLASTIC, TQFP-128 |

| 文件頁數(shù): | 14/40頁 |

| 文件大小: | 644K |

| 代理商: | CY7C43686AV-15AC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

CY7C43646AV

CY7C43666AV

CY7C43686AV

Document #: 38-06026 Rev. *C

Page 14 of 40

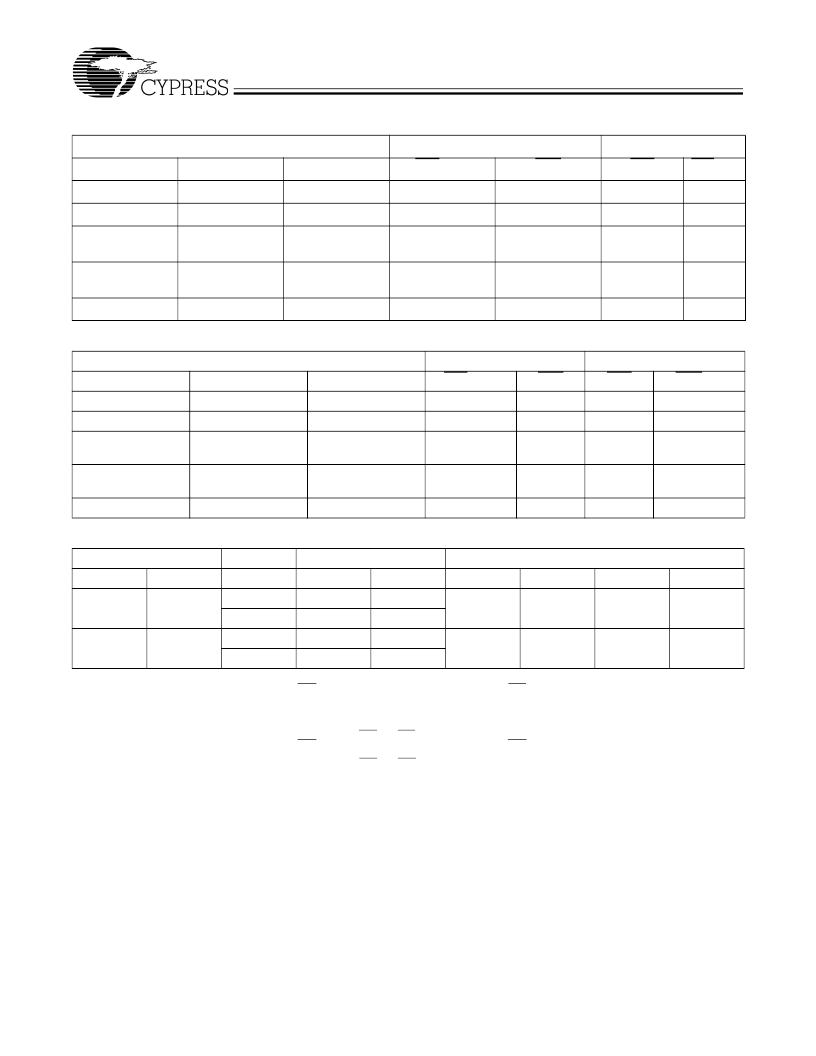

Table 5. FIFO1 Flag Operation (CY Standard and FWFT modes)

Number of Words in FIFO Memory

[61, 3, 4, 5, 6]

Synchronized to CLKB

Synchronized to CLKA

CY7C43646AV

CY7C43666AV

CY7C43686AV

EFB/ORB

AEB

AFA

FFA/IRA

0

0

0

L

L

H

H

1

–

X1

1

–

X1

1

–

X1

H

L

H

H

(X1 + 1) to [1024

–

(Y1

–

1)]

(X1 + 1) to [4096

–

(Y1 + 1)]

(X1 + 1) to [16384

–

(Y1 + 1)]

H

H

H

H

(1024

–

Y1) to

1023

(4096

–

Y1) to

4095

(16384

–

Y1) to

16383

H

H

L

H

1024

4096

16384

H

H

L

L

Table 6. FIFO2 Flag Operation (CY Standard and FWFT modes)

Number of Words in FIFO Memory

[61, 4, 5, 7, 8]

CY7C43646AV

CY7C43666AV

0

0

1

–

X2

1

–

X2

(X2 + 1) to [1024

–

(Y2 + 1)]

(Y2 + 1)]

(1024

–

Y2) to 1023

(4096

–

Y2) to 4095

Synchronized to CLKA

EFA/ORA

L

H

H

Synchronized to CLKC

AFC

H

H

H

CY7C43686AV

0

1

–

X2

(X2 + 1) to [16384

–

(Y2 + 1)]

(16384

–

Y2) to

16383

16384

AEA

L

L

H

FFC/IRC

H

H

H

(X2 + 1) to [4096

–

H

H

L

H

1024

4096

H

H

L

L

Table 7. Data Size Table for Word Writes to FIFO2

Size Mode

[9]

SIZE

BE

L

H

Write No.

Data Written to FIFO2

C

9

–

17

A

C

C

A

Data Read From FIFO2

A

18

–

26

B

C

0

–

8

B

D

D

B

A

27

–

35

A

A

9

–

17

C

A

0

–

8

D

1

2

1

2

L

L

A

B

C

D

Notes:

3.

X1 is the almost-empty offset for FIFO1 used by AEB. Y1 is the almost-full offset for FIFO1 used by AFA. Both X1 and Y1 are selected during a FIFO1 reset

or port A programming.

When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

Data in the output register does not count as a

“

word in FIFO memory

”

. Since in FWFT Mode, the first word written to an empty FIFO goes unrequested to the

output register (no Read operation necessary), it is not included in the FIFO memory count.

The ORB and IRA functions are active during FWFT mode; the EFB and FFA functions are active in CY Standard mode.

X2 is the almost-empty offset for FIFO2 used by AEA. Y2 is the almost-full offset for FIFO2 used by AFC. Both X2 and Y2 are selected during a FIFO2 reset

or port A programming.

The ORA and IRC functions are active during FWFT mode; the EFA and FFC functions are active in CY Standard mode.

BE is selected at Master Reset. SIZEC must be static throughout device operation.

4.

5.

6.

7.

8.

9.

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C43686AV-7AC | 3.3V 1K 4K 16K x 36 x 18 x 2 Tri Bus FIFO |

| CY7C43686AV-10AI | 3.3V 1K 4K 16K x 36 x 18 x 2 Tri Bus FIFO |

| CY7C43686AV-10AC | 3.3V 1K 4K 16K x 36 x 18 x 2 Tri Bus FIFO |

| CY7M194-10DC | x4 SRAM Module |

| CY7M194-12DC | x4 SRAM Module |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C43686AV-7AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Triple Depth/Width Tri-Bus 16K x 36/16K x 18 x 2 128-Pin TQFP |

| CY7C439-40DMB | 制造商:Cypress Semiconductor 功能描述: |

| CY7C441-14JC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Width Uni-Dir 512 x 9 32-Pin PLCC |

| CY7C441-30JC | 制造商:Cypress Semiconductor 功能描述:FIFO, 512 x 9, Synchronous, 32 Pin, Plastic, PLCC |

| CY7C441-30JI | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。