- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376602 > DDP3300A (MICRONAS SEMICONDUCTOR HOLDING AG) Single-Chip Display and Deflection Processor PDF資料下載

參數(shù)資料

| 型號: | DDP3300A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Single-Chip Display and Deflection Processor |

| 中文描述: | 單芯片顯示器和偏轉(zhuǎn)處理器 |

| 文件頁數(shù): | 4/53頁 |

| 文件大小: | 1767K |

| 代理商: | DDP3300A |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

PRELIMINARY DATA SHEET

DDP 3300 A

MICRONAS INTERMETALL

4

DDP 3300 A, Display and Deflection Processor

50/60 Hz

(68-pin PLCC or 64-pin PSDIP Package)

Note:

Revision bars indicate significant changes to the pre-

vious version, ed. 6251-421-1AI, Advance Information,

dated Feb. 9, 1996.

1. Introduction

The DDP 3300 A is a single-chip digital display and

deflection processor in 0.8

μ

m CMOS technology for

high quality back-end applications in 50/60 Hz TV sets

with 4:3 or 16:9 picture tubes. It can be combined with

members of the DIGIT 3000 IC family (VPC 3200 A,

VPC 3201 B, TPU 3040) or it can be used with third par-

ty products. One IC contains the entire video component

and deflection processing and forms the heart of a mod-

ern color TV. Its performance and complexity allow the

user to standardize his product development. Hardware

and software applications can profit from the modularity,

as well as manufacturing, system support or mainte-

nance. The main features are

– single 5 V power supply

– low cost, high performance all digital video processing

– black-level expander

– dynamic peaking

– soft limiter (gamma correction)

– color transient improvement

– programmable RGB matrix

– scan velocity modulation output

– picture frame generator

– additional analog RGB/fastblank input

– Prio interface

– various digital interfaces

– high performance H/V deflection

– separate ADC for tube measurements

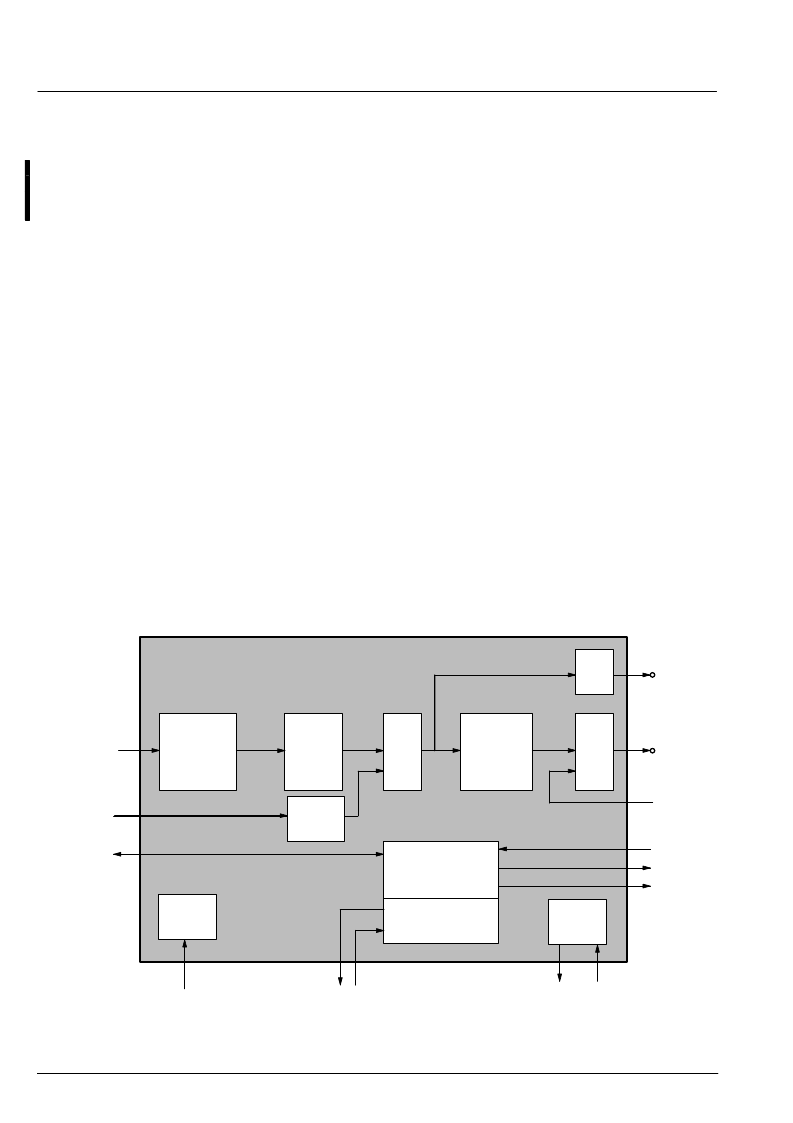

1.1. System Architecture

Open architecture is the key word to the new DSP gener-

ation. Flexible standard building blocks have been de-

fined that offer continuity and transparency of the entire

system. Two main modules were defined:

– Video Processor and

– Display and Deflection Processor.

They were designed as separate ICs. Their partitioning

permits a variety of IC configurations with the aim to sat-

isfy the particular requirements of different applications.

Both, analog and digital interfaces, support state-of-the

art TV receivers as well as other environments. Fig. 1–1

shows the block diagram of the single-chip Display and

Deflection Processor.

Y features

C features

YCrCb

4:2:2

H/V deflection

DACs

RGB

Prio

RGB

switch

dig.

scan

vel.

mod.

RGB

switch

analog

RGB

out

RGB/

Fbl

in

Hflyb.

Hdrive

V & E/W

SVM

digital

RGB

matrix

color

lookup

table

I

2

C

interface

SDA, SCL

3 x DAC

(10 bit)

and

tube

control

sense

input

range

switch

1 & 2

FPDAT

front

sync

main

sync

timing generator

Fig. 1–1:

Display and Deflection Processor

measu-

rement

ADC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DDP3310B | Display and Deflection Processor |

| DDR-TJS-T2 | LED AlInGaP |

| DD0-SJS-S1 | LED AlInGaP |

| DD0-SJS-S2 | LED AlInGaP |

| DD0-SJS-T1 | LED AlInGaP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DDP3300A(DIP64) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

| DDP3300A(PLCC68) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TV/Video Signal Processor |

| DDP3300A(SDIP64) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TV/Video Signal Processor |

| DDP3300AD3 | 制造商:MICRONAS 功能描述:New |

| DDP3300APSD3 | 制造商:MICRONAS 功能描述:New |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。