- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376767 > DM4M32SJ-15 Enhanced DRAM (EDRAM) Module PDF資料下載

參數(shù)資料

| 型號: | DM4M32SJ-15 |

| 英文描述: | Enhanced DRAM (EDRAM) Module |

| 中文描述: | 增強的DRAM(eDRAM內(nèi)存)模塊 |

| 文件頁數(shù): | 1/24頁 |

| 文件大小: | 164K |

| 代理商: | DM4M32SJ-15 |

DM4M32SJ

4Mbx 32 EnhancedDRAMSIM

M

ProductSpecifcaton

1996 Enhanced Memory Systems Inc.,

1850 Ramtron Drive, Colorado Springs, CO80921

Telephone

(800) 545-DRAM;

Fax

(719) 488-9095; http://wwwcsn.net/ramtron/enhanced

38-2110-002

The information contained herein is subject to change wthout notice. Enhanced reserves the right

to change or discontinue this product wthout notice.

Features

I

Integrated 2,048 x 32 SRAMCache RowRegister Allows 12ns

Access RandomReads Wthin the Page

I

Interleaved SRAMCache for 8ns Burst Reads

I

30ns DRAMArray for Fast RandomAccess to Any Page

I

Utra-Fast Integrated 8Kbyte-Wde DRAMto Cache Bus

for 454-Gbyte/sec Cache Fill Bandwdth

I

On-Chip Write Posting and Fast Page Mode Operation Allows

12ns Writes and Burst Writes

I

On-Board Address and Control Buffering

I

LowPower Self Refresh Mode Option

Description

The Enhanced Memory Systems 16MB EDRAMSIMMmodule

provides a single memory module solution for the main memory or

local memory of fast PCs, workstations, servers, and other high

performance systems. Due to its fast 12ns cache rowregister, the

EDRAMmemory module supports zero-wait-state burst read

operations at up to 66MHz bus rates in a non-interleave configuration

and >100MHz bus rates wth a two-way interleave configuration.

On-chip write posting and fast page mode operation supports

12ns write and burst write operations. On a cache mss, the fast

DRAMarray reloads the entire 8Kbyte cache over an 8Kbyte-wde bus

in 18ns for an effective bandwdth of 454 Gbytes/sec. This means very

lowlatency and fewer wait states on a cache mss than a non-

integrated cache/DRAMsolution. The JEDEC compatible SIMM

configuration allows a single memory controller to be designed to

support either JEDEC slowDRAMs or high speed EDRAMs to provide

a simple upgrade path to higher systemperformance.

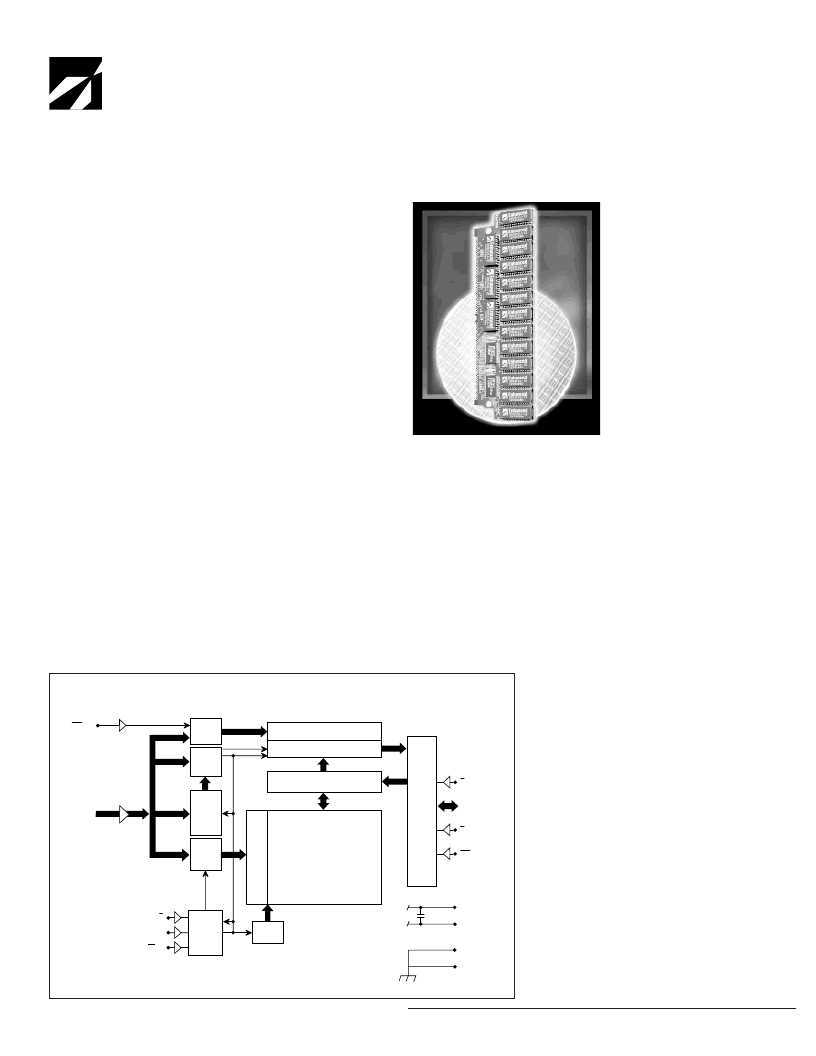

Architecture

The DM4M32SJ achieves

4Mb x 32 density by mounting

32 4Mx 1 EDRAMs, packaged

in 28-pin plastic SOJ packages

on both sides of the multi-

layer substrate. Four buffers

have been added to reduce the

loading on the address and

control lines. The buffers have

balanced output current levels

and current limting resistors.

These offer lowground

bounce, mnimal undershoot,

and controlled fall times.

The EDRAMmemory

module architectureis very

simlar to a standard 16MB DRAMmodule wth the addition of an

integrated cache and on-chip control which allows it to operate much

like a page mode or static column DRAM

The EDRAMs SRAMcache is integrated into the DRAMarray as

tightly coupled rowregisters. Memory reads always occur fromthe

cache rowregister. When the on-chip comparator detects a page hit,

only the SRAMis accessed and data is available in 12ns fromcolumn

address. When a page read mss is detected, the entire newDRAMrow

is updated into the cache and data is available at the output all wthin

a single 30ns access. Subsequent reads wthin the page (burst reads,

local instructions, or data) wll continue at 12ns cycle time. Since reads

occur fromthe SRAMcache, DRAMprecharge can occur simultaneously

wthout degrading performance. The on-chip refresh counter wth

independent refresh bus allows the EDRAMto

be refreshed during cache reads.

Memory writes are internally posted in

12ns and directed to the DRAMarray During

a write hit, the on-chip address comparator

activates a parallel write path to the SRAM

cache to maintain coherency The EDRAM

delivers 12ns cycle page mode memory writes.

Memory writes do not affect the contents of

the cache rowregister except during a cache

hit.

By integrating the SRAMcache as row

registers in the DRAMarray and keeping the

on-chip control simple, the EDRAMis able to

provide superior performance over standard

slowDRAMs.

C

1-36

CAL

A

0-10

W/R

F

V

V

Sense Amps

& Column Write Select

Column Decoder

Add

Latch

CC

SS

PD

PD16M

2048 X 32 Cache (Row Register)

Array

16Mbyte

G

S

WE

DQ

0-31

CAdd

Latch

Comp

Last

Add

Latch

CI/O

and

Latches

Refresh

Counter

R

Row Add

Rand

Control

0-3

RE

0,2

A

0-10

A

0-9

DM4M32SJ Functional Dagram

Enhanced

Memory Systems Inc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM4M32SJ-15L | Enhanced DRAM (EDRAM) Module |

| DM4M32SJ6-12 | Enhanced DRAM (EDRAM) Module |

| DM4M32SJ6-12L | Enhanced DRAM (EDRAM) Module |

| DM4M32SJ6-15 | Enhanced DRAM (EDRAM) Module |

| DM4M32SJ6-15L | Enhanced DRAM (EDRAM) Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM4PRTR | 制造商:Siemens 功能描述: |

| DM4S6B00F/17 | 制造商:NXP Semiconductors 功能描述:DVD-R 16X 100PK Spindle 制造商:NXP Semiconductors 功能描述:DVD-R 16X SPINDLE 100PK |

| DM4S6B25F/17 | 制造商:NXP Semiconductors 功能描述:DVD-R 16X 25PK Spindle 制造商:NXP Semiconductors 功能描述:DVD-R 16X SPINDLE 25PK |

| DM4S6B50F/17 | 制造商:NXP Semiconductors 功能描述:DVD-R 16X 50PK Spindle |

| DM4T1200 | 制造商:Lovato Electric Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。