- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376801 > DM8108 (Electronic Theatre Controls, Inc.) 8 port 10/100M Fast Ethernet Switching Controller PDF資料下載

參數(shù)資料

| 型號: | DM8108 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 8 port 10/100M Fast Ethernet Switching Controller |

| 中文描述: | 8端口10/100M快速以太網(wǎng)交換控制器 |

| 文件頁數(shù): | 23/35頁 |

| 文件大小: | 371K |

| 代理商: | DM8108 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

DM8108

8 port 10/100M Fast Ethernet Switching Controller

Preliminary 23

Version: DM8108-DS-P02

November 25, 1999

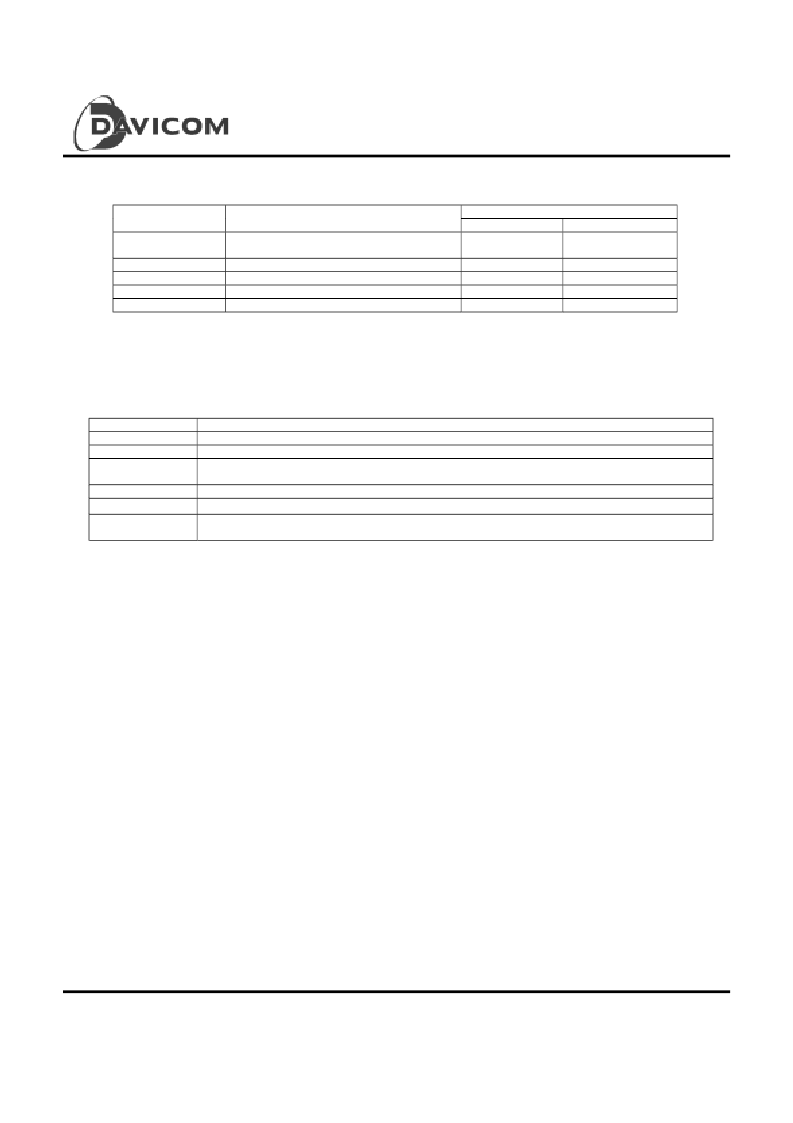

DM8108 DRAM Address Mapping

Memory Size

1M Byte

028000 – 0FFFFF

Queue & Buffers

Description

2M Byte

028000 – 1FFFFF

Receive Buffer

864KB ( 576 blocks)

1872KB (1248blocks) + unused

8KB

4KB

20KB

128KB

ACC Count

Reserved

TDR queue

Address Table

026000 – 027FFF

025000 – 025FFF

020000 – 024FFF

000000 – 01FFFF

027000 – 027FFF

025000 – 025FFF

020000 – 024FFF

000000 – 01FFFF

Address Table

The Address Table structure occupies 128K bytes of

memory and is controlled and initialized by the

DM8108. Following RESET, the DM8108 initializes

Field

Description

V

Valid – Indicates a valid entry; 0 – Not Valid, 1 – valid.

Address (47:0)

Source MAC address. Unicast address only

Port Number – indicates which of the 3-port in a DM8108 is associated with this source address.

0h – 1h: Port 0 –Port 1 (2 Ethernet ports); 2h: Expansion Port.

Reserved

Device #

Device number—indicate which device in the switching system is associated with this source address

4-bit Tag—used to identify the update sequence. If the entry-block(4-entry) pointed by a MAC address index are

all occupied, the entry that has oldest time stamp will be replaced.

the Address Table by invalidating the Valid bit of all

entries.

Port #

Time Stamp

Packet Forwarding

The following sections describe the procedures for

forwarding packets under different situations:

Forwarding a Uni-cast packet to a local Ethernet

port

The incoming packet is fed to the Rx FIFO and is

transferred to an empty block in the Receive Buffer

area of DRAM. The switching engine will claim the

block by setting the Empty List not empty. In case of

collision or FIFO overflow, transfer error etc. , the

engine has to reset the Empty List associated with the

block.

In parallel, an address recognition cycle will be

performed for both the destination and source address.

The DM8108 will use SA to learn a new or changed

address entry. The DA will point to an entry that

specifies the local port’s number.

At the end of reception of an error-free packet, the

packet information is written to the appropriate port’s

transmit descriptor. This information includes the

Byte Count, Receive block address which points to

the Write Pointer, and the Priority indication.

The Write Pointer of the outgoing port’s transmit

descriptor is incremented. The target port prepare for

transmission whenever the Write Pointer and the

Read pointer are not equal.

The engine resolves the priority issue and fills the Tx

FIFO before starting the transmission. If any Tx

FIFO under run situation happens, the MAC has to

force the packet “Bad” and inform the engine to retry.

At the end of the good transmit process, the target

port increments the Read Pointer. The Engine clears

the appropriate bit in the Empty List.

相關PDF資料 |

PDF描述 |

|---|---|

| DM8121W | 8-Input Digital Multiplexer |

| DM8123N | 2-Input Digital Multiplexer |

| DM7123J | 2-Input Digital Multiplexer |

| DM7123W | 2-Input Digital Multiplexer |

| DM8123W | 2-Input Digital Multiplexer |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DM-810A | 功能描述:數(shù)字萬用表 DMM,TRMS 1000V AC/DC 600mA to 10A RoHS:否 制造商:Tektronix 產(chǎn)品:Multimeters 類型:Bench 準確性:0.04 % 電壓范圍:2 V to 2 kV 電阻范圍: 電容范圍: 顯示計數(shù): 頻率:10 Hz to 45 Hz, 850 Hz to 1 MHz 測距: 真均方根值: 數(shù)據(jù)保持: |

| DM-810A-C | 功能描述:數(shù)字萬用表 DMM,TRMS 1000V AC/DC 600mA to 10A, CALIB RoHS:否 制造商:Tektronix 產(chǎn)品:Multimeters 類型:Bench 準確性:0.04 % 電壓范圍:2 V to 2 kV 電阻范圍: 電容范圍: 顯示計數(shù): 頻率:10 Hz to 45 Hz, 850 Hz to 1 MHz 測距: 真均方根值: 數(shù)據(jù)保持: |

| DM8121J/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Input Digital Multiplexer |

| DM8121N/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Input Digital Multiplexer |

| DM8121N/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Input Digital Multiplexer |

發(fā)布緊急采購,3分鐘左右您將得到回復。