- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376803 > DM9338 PDF資料下載

參數(shù)資料

| 型號: | DM9338 |

| 文件頁數(shù): | 20/43頁 |

| 文件大小: | 509K |

| 代理商: | DM9338 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

DM9331

100 Mbps Twisted Pair/Fiber Ethernet Media Converter Chip

20

Preliminary

Version: DM9331-DS-P02

September 21, 2001

0.7

Collision test

0,RW

Collision test:

1 = Collision test enabled. When set, this bit will cause the COL

signal to be asserted in response to the assertion of TXEN

0 = Normal operation

Reserved:

Write as 0, ignore on read

0.6-0.0

Reserved

0,RO

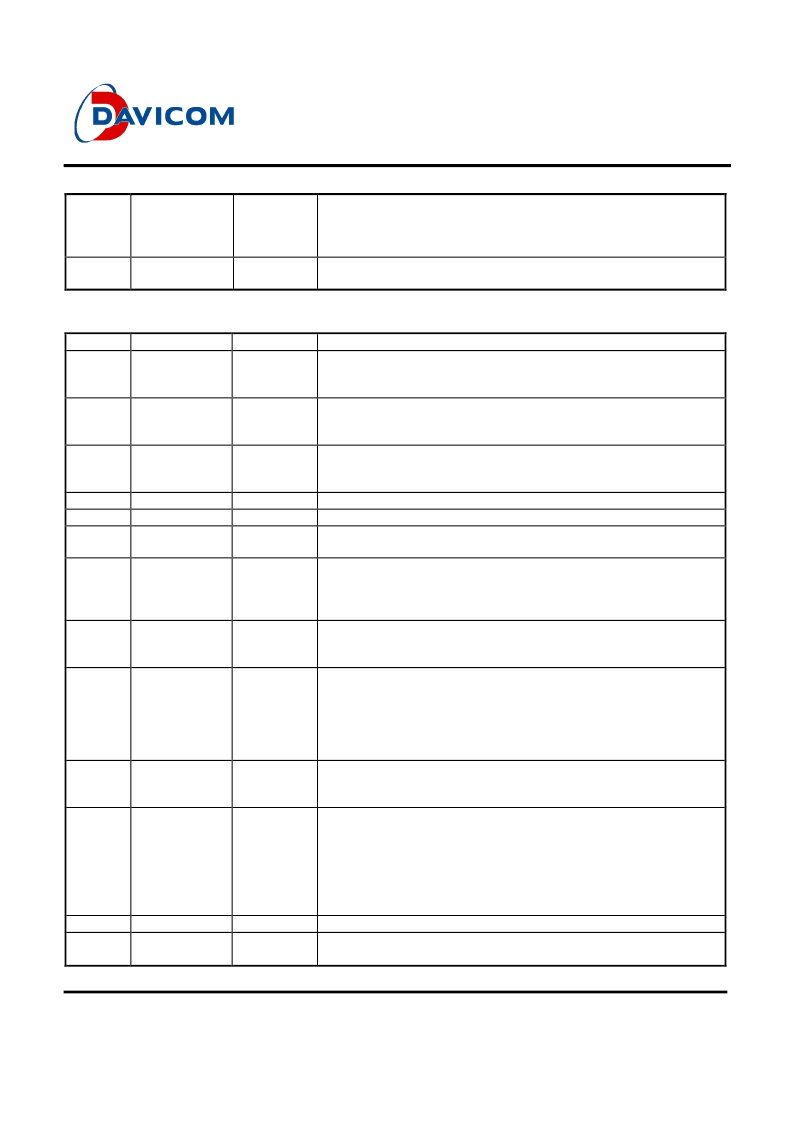

Basic Mode Status Register (BMSR) - 01

Bit

1.15

Bit Name

100BASE-T4

Default

0,RO/P

Description

100BASE-T4 capable:

1 = DM9331 is able to perform in 100BASE-T4 mode

0 = DM9331 is not able to perform in 100BASE-T4 mode

100BASE-TX full duplex capable:

1 = DM9331 is able to perform 100BASE-TX in full duplex mode

0 = DM9331 is not able to perform 100BASE-TX in full duplex mode

100BASE-TX half duplex capable:

1 = DM9331 is able to perform 100BASE-TX in half duplex mode

0 = DM9331 is not able to perform 100BASE-TX in half duplex mode

Reserved

Reserved

Reserved:

Write as 0, ignore on read

MII frame preamble suppression:

1 = PHY will accept management frames with preamble suppressed

0 = PHY will not accept management frames with preamble

suppressed

Auto-negotiation complete:

1 = Auto-negotiation process completed

0 = Auto-negotiation process not completed

Remote fault:

1 = Remote fault condition detected (cleared on read or by a chip

reset). Fault criteria and detection method is DM9331

implementation specific. This bit will set after the RF bit in the

ANLPAR (bit 13, register address 05) is set

0 = No remote fault condition detected

Auto configuration ability:

1 = DM9331 is able to perform auto-negotiation

0 = DM9331 is not able to perform auto-negotiation

Link status:

1 = Valid link is established (for 100Mbps operation)

0 = Link is not established

The link status bit is implemented with a latching function, so that the

occurrence of a link failure condition causes the link status bit to be

cleared and remain cleared until it is read via the management

interface

Reserved

Extended capability:

1 = Extended register capable. 0 = Basic register capable only

1.14

100BASE-TX

full duplex

1,RO/P

1.13

100BASE-TX

half duplex

1,RO/P

1.12

1.11

1.10-1.7

Reserved

Reserved

Reserved

0,RO/P

0,RO/P

0,RO

1.6

MF preamble

suppression

0,RO

1.5

Auto-

negotiation

Complete

Remote fault

0,RO

1.4

0,

RO/LH

1.3

Auto-

negotiation

ability

Link status

1,RO/P

1.2

0,RO/LL

1.1

1.0

Reserved

Extended

capability

0,RO/LH

1,RO/P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9334 | 8-Bit Addressable Latch |

| DM9334N | 8-Bit Addressable Latch |

| DM9348 | |

| DM93L00 | |

| DM93L01 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9338 WAF | 制造商:Texas Instruments 功能描述: |

| DM9338J/883 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Register File |

| DM9338N | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:8-Bit Multiple Port Register |

| DM9338W/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DM933N | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。