- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376836 > DP84422N DRAM Controller PDF資料下載

參數(shù)資料

| 型號: | DP84422N |

| 英文描述: | DRAM Controller |

| 中文描述: | DRAM控制器 |

| 文件頁數(shù): | 20/46頁 |

| 文件大小: | 644K |

| 代理商: | DP84422N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

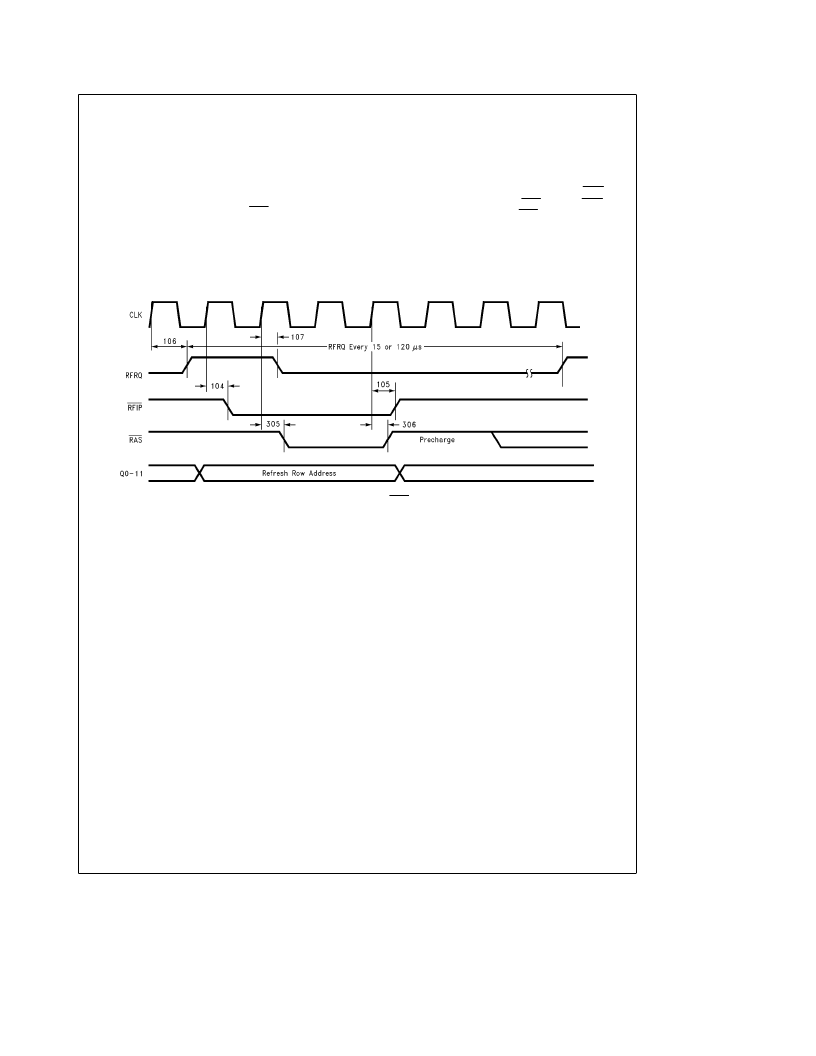

6.0 Refresh Modes

The DP8440/41 support auto-internal refresh, and external-

ly control refresh. The DP8440/41 arbitrates between re-

freshes and accesses and guarantees precharge timings af-

ter every access and refresh. The DRAM controller will nev-

er interrupt an access in progress to do a refresh, nor will it

interrupt a refresh in progress when an access is requested.

After every refresh the DRAM controller will guarantee the

programmed precharge time before RAS can assert for a

new access or for a second refresh. The refresh period can

be programmed for 15

m

s or for 120

m

s.

6.1 AUTO-INTERNAL REFRESH

This refresh scheme is completely transparent to the CPU.

The DP8440/41 will refresh the DRAM every 15

m

s or

120

m

s, depending on the programming selection. When the

refresh counter expires (every 15

m

s or 120

m

s) the RFRQ

output asserts. On the next rising edge of clock RFIP as-

serts and, one clock period later, RASs assert. RFIP ne-

gates on the same clock edge that RASs negate. If the user

is doing long page or burst accesses, the DP8440/41 will

keep track of up to 6 missed refreshes. At the end of the

access the DRAM controller will burst refresh the locations

missed during the access.

TL/F/11718–10

FIGURE 14. Autointernal Refresh (2T of RAS Low and Precharge)

20

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DP84432J | DRAM Controller |

| DP84432N | DRAM Controller |

| DP8472 | Floppy Disk Controller |

| DP8472J | Floppy Disk Controller |

| DP8472N | Floppy Disk Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DP84422N/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84422N/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84432J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84432J/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84432N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。