- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1914 > DS2181AQN+ (Maxim Integrated Products)IC TXRX CEPT PRIMARY RATE 44PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | DS2181AQN+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 27/32頁 |

| 文件大小: | 0K |

| 描述: | IC TXRX CEPT PRIMARY RATE 44PLCC |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 26 |

| 類型: | 收發(fā)器 |

| 驅(qū)動(dòng)器/接收器數(shù): | 1/1 |

| 規(guī)程: | CEPT |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 44-PLCC(16.59x16.59) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁

DS2181A

4 of 32

NOTES:

1. These output status pins are only available on the DS2181AQ.

2. If the TEST pin is tied low and CCR.1=0, then these pins will be tri–stated.

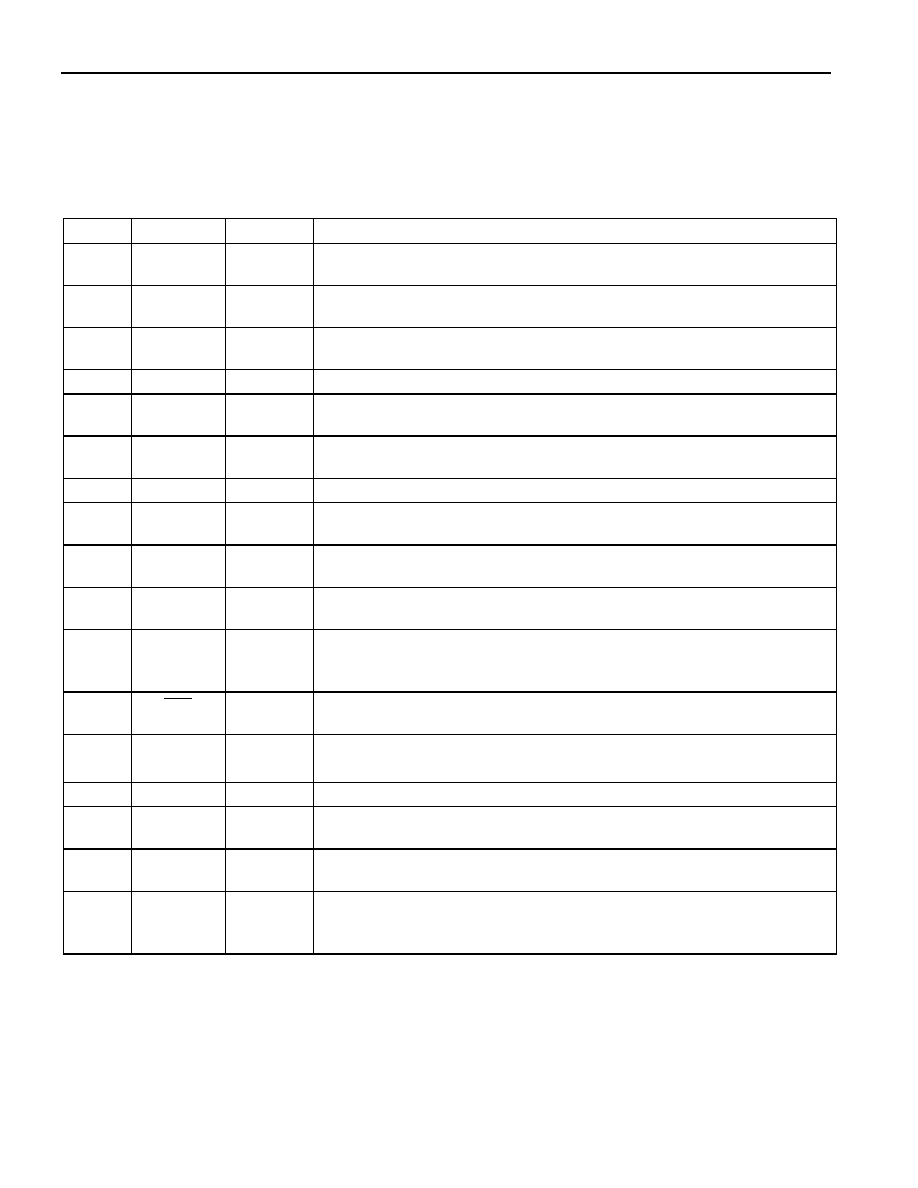

RECEIVE PIN DESCRIPTION (40-PIN DIP ONLY) Table 2B

PIN

SYMBOL

TYPE

DESCRIPTION

21

RRA

O

Receive Remote Alarm. Transitions high when alarm detected;

returns low when alarm cleared.

22

RMDA

O

Receive Distant Multiframe Alarm. Transitions high when alarm

detected; returns low when alarm cleared.

23

RAF

O

Receive Alignment Frame. High during frames containing the frame

alignment signal, low otherwise.

24

RCLK

I

Receive Clock. 2.048 MHz primary clock.

25

RCHCLK

O

Receive Channel Clock. 256 kHz clock, identifies timeslot

boundaries; useful for serial-to-parallel conversion of channel data.

26

RSER

O

Receive Channel Clock. 256 kHz clock, identifies timeslot

boundaries; useful for serial-to-parallel conversion of channel data.

27

RFSYNC

O

Receive Frame Sync. Trailing edge indicates start of frame.

28

RMSYNC

O

Receive Multiframe Sync. Low-high transition indicates start of

CAS multiframe; held high during frame 0.

29

RSD

O

Receive Signaling Data. Extracted timeslot 16 data; updated on

rising edge of RCLK.

30

RSTS

O

Receive Signaling Timeslot. High during timeslot 16 of every frame,

low otherwise.

31

RCSYNC

O

Receive CRC4 Sync. Low-high transition indicates start of CRC4

multiframe; held high during CRC4 frames 0 through 7 and held low

during frames 8 through 15.

33

RST

I

Reset. Must be asserted during device power-up and when changing

to/from the hardware mode.

34

35

RPOS

RNEG

I

Receive Bipolar Data. Sampled on falling edges of RCLK. Tie

together to receive NRZ data and disable BPV monitor circuitry.

36

RCL

O

Receive Carrier Loss. Low-high transition indicates loss of carrier.

37

RBV

O

Receive Bipolar Violation. Pulses high during detected bipolar

violations.

38

RFER

O

Receive Frame Error. Pulses high when frame alignment, CAS

multiframe alignment or CRC4 words received in error.

39

RLOS

O

Receive Loss of Sync. Indicates synchronizer status; high when

frame, CAS and/or CRC4 multiframe search underway, low

otherwise.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS2186S/T&R | IC TRANSMIT LINE INTERFC 20-SOIC |

| DS2188SN/TRL | IC ATTEN JTR T1/CEPT IND 16-SOIC |

| DS2196LN+ | IC FRAMER DUAL T1 LIU 100-LQFP |

| DS21FF42 | IC FRAMER T1 4X4 16CH 300-BGA |

| DS21FF44 | IC FRAMER E1 4X4 16CH 300-BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS2181AQN/T&R | 制造商:Maxim Integrated Products 功能描述:CEPT TRANSCEIVER-PLCC-IND-TRL - Tape and Reel 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述:IC TXRX CEPT PRIM RATE IN 44PLCC 制造商:Maxim Integrated Products 功能描述:Network Controller & Processor ICs CEPT Primary Rate Transceiver |

| DS2181AQN/T&R+ | 制造商:Maxim Integrated Products 功能描述:CEPT TRANSEIVER PLCC IND TRL LF - Tape and Reel |

| DS2181AQN/T&R | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC CEPT Primary Rate Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2181AQN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC CEPT Primary Rate Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2181AQN+T&R | 制造商:Maxim Integrated Products 功能描述: 制造商:Maxim Integrated Products 功能描述:CEPT TRNSCVR 1TX 1RX 44PLCC - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC TXRX CEPT PRIMARY RATE 44PLCC 制造商:Maxim Integrated Products 功能描述:Network Controller & Processor ICs CEPT Primary Rate Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。