- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1915 > DS3150TN (Maxim Integrated Products)IC LIU T3/E3/STS-1 IND 48-TQFP PDF資料下載

參數(shù)資料

| 型號: | DS3150TN |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 15/28頁 |

| 文件大小: | 0K |

| 描述: | IC LIU T3/E3/STS-1 IND 48-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS |

| 產(chǎn)品變化通告: | Product Discontinuation 20/Feb/2012 |

| 標(biāo)準(zhǔn)包裝: | 250 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 1/1 |

| 規(guī)程: | DS3 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-LQFP |

| 供應(yīng)商設(shè)備封裝: | 48-LQFP(7x7) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

DS3150

22 of 28

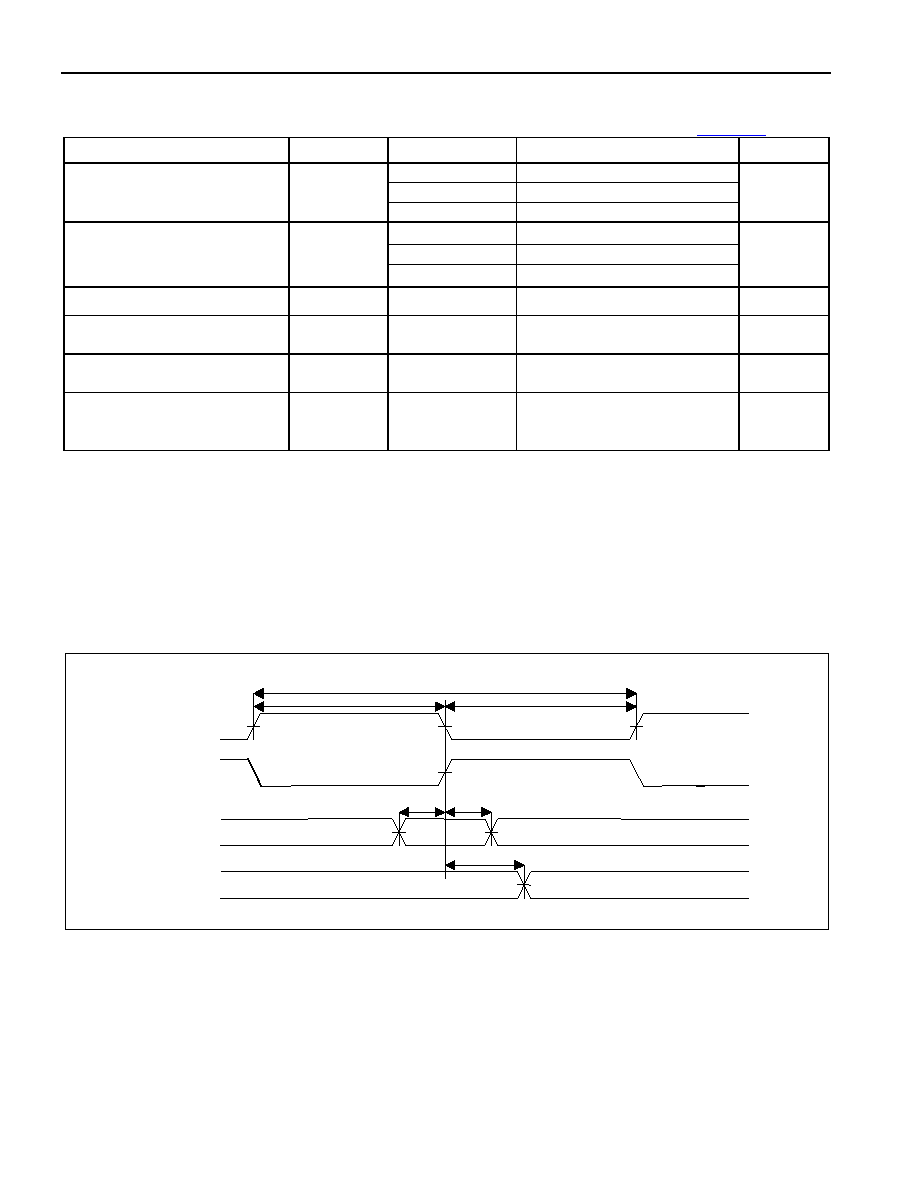

FRAMER INTERFACE TIMING

(VDD = 3.3V

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

(Note 4)

22.4

(Note 5)

29.1

RCLK/TCLK Clock Period

t1

(Note 6)

19.3

ns

(Note 4)

9.0

11.2

13.4

(Note 5)

11.6

14.5

17.4

RCLK Clock High/Low Time

t2, t3

(Note 6)

7.7

9.6

11.5

ns

TCLK Clock High/Low Time

t2, t3

7

ns

TPOS/TNRZ, TNEG to TCLK

Setup Time

t4

2

ns

TPOS/TNRZ, TNEG Hold

Time

t5

2

ns

RCLK to RPOS/RNRZ Valid,

RNEG/RLCV Valid, State

Change on PRBS

t6

(Notes 7, 8)

2

6

ns

Note 4:

DS3 mode.

Note 5:

E3 mode.

Note 6:

STS-1 mode.

Note 7:

In normal mode, TPOS/TNRZ and TNEG are sampled on the rising edge of TCLK and RPOS/RNRZ and RNEG/RLCV are

updated on the falling edge of RCLK.

Note 8:

In inverted mode, TPOS/TNRZ and TNEG are sampled on the falling edge of TCLK and RPOS/RNRZ and RNEG/RLCV are

updated on the rising edge of RCLK.

Figure 3-1. Framer Interface Timing Diagram

RCLK (normal mode),

TCLK (inverted mode)

TPOS/TNRZ, TNEG

RPOS/RNRZ,

RNEG/RLCV, PRBS

t4

t5

t6

t1

t2

t3

TCLK (normal mode),

RCLK (inverted mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3154N+ | IC LIU DS3/E3/STS-1 QD 144CSBGA |

| DS3164+ | IC ATM/PACKET PHY QUAD 400-BGA |

| DS3170+ | IC TXRX DS3/E3 100-CSBGA |

| DS3172N+ | IC TXRX DS3/E3 DUAL 400-BGA |

| DS3181N+ | IC ATM/PACKET PHY W/LIU 400PBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3150TN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3150TN1 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS3150TNC1 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3150TNC1+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3151 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Single DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。