- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19910 > EPC2TI32N (Altera)IC CONFIG DEVICE 1.6MBIT 32-TQFP PDF資料下載

參數(shù)資料

| 型號: | EPC2TI32N |

| 廠商: | Altera |

| 文件頁數(shù): | 6/26頁 |

| 文件大小: | 0K |

| 描述: | IC CONFIG DEVICE 1.6MBIT 32-TQFP |

| 產(chǎn)品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 250 |

| 系列: | EPC |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲容量: | 1.6Mb |

| 電源電壓: | 3 V ~ 3.6 V,4.5 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 32-TQFP |

| 供應(yīng)商設(shè)備封裝: | 32-TQFP(7x7) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 604 (CN2011-ZH PDF) |

| 其它名稱: | 544-1648 |

Page 14

IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing

Configuration Devices for SRAM-Based LUT Devices

January 2012

Altera Corporation

IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing

The EPC2 device provides JTAG BST circuitry that complies with the IEEE Std.

1149.1-1990 specification. You can perform JTAG BST before or after configuration, but

not during configuration. Table 6 lists the JTAG instructions supported by the EPC2

device.

f For more information, refer to AN39: IEEE 1149.1 JTAG Boundary-Scan Testing in Altera

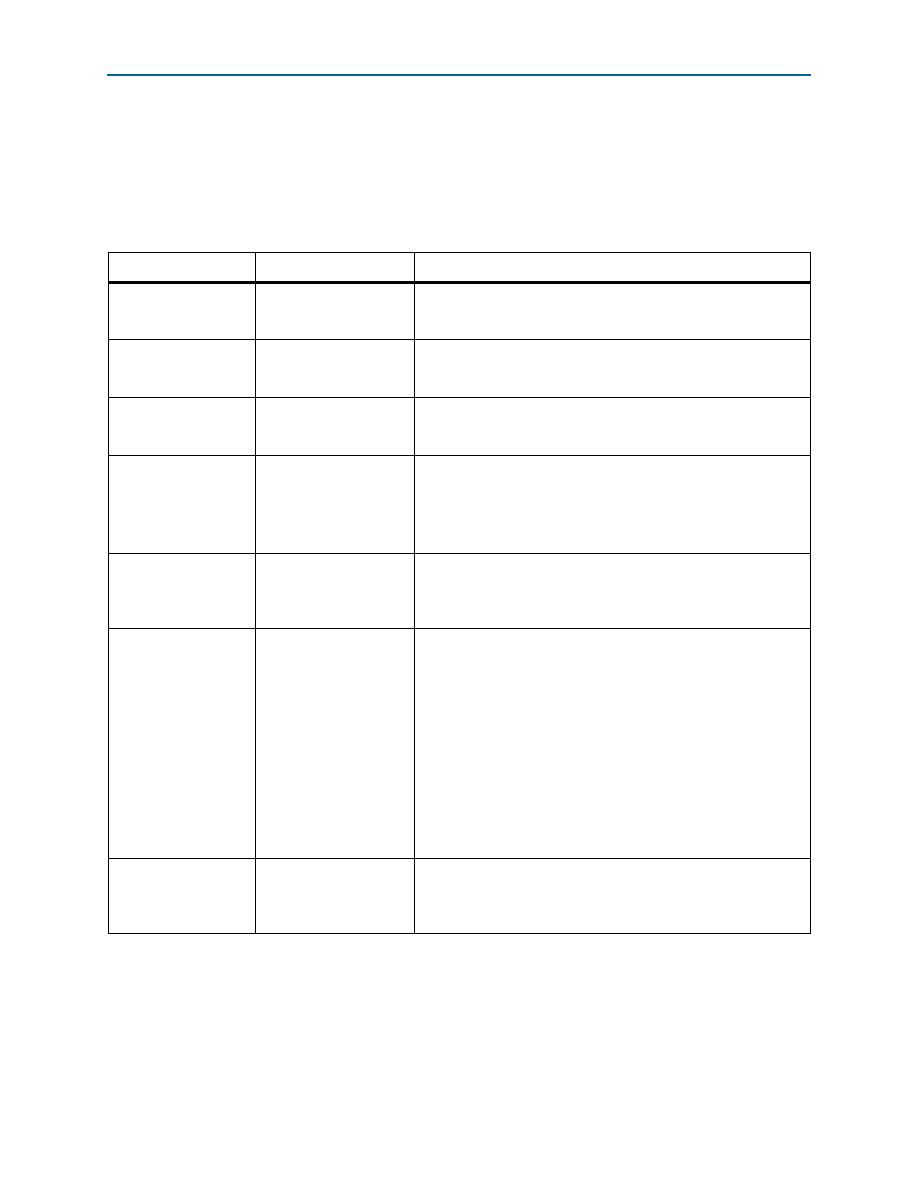

Table 6. EPC2 Device JTAG Instructions

JTAG Instruction

OPCODE

Description

SAMPLE/PRELOAD

00 0101 0101

Allows a snapshot of a signal at the device pins to be captured and

examined during normal device operation and permits an initial data

pattern output at the device pins.

EXTEST

00 0000 0000

Allows the external circuitry and board-level interconnections to be

tested by forcing a test pattern at the output pins and capturing

results at the input pins.

BYPASS

11 1111 1111

Places the 1-bit bypass register between the TDI and TDO pins,

which allows the BST data to pass synchronously through a selected

device to adjacent devices during normal device operation.

IDCODE

00 0101 1001

Selects the device IDCODE register and places it between the TDI

and TDO pins, allowing the device IDCODE to be serially shifted out of

the TDO pin. The device IDCODE for the EPC2 configuration device is

shown below:

0000 0001000000000010 00001101110 1

USERCODE

00 0111 1001

Selects the USERCODE register and places it between the TDI and

TDO

pins, allowing the USERCODE to be serially shifted out of the

TDO

pin. The 32-bit USERCODE is a programmable user-defined

pattern.

INIT_CONF

00 0110 0001

Initiates the FPGA re-configuration process by pulsing the

nINIT_CONF

pin low, which is connected to the FPGAs nCONFIG

pins. After this instruction is updated, the nINIT_CONF pin is pulsed

low when the JTAG state machine enters the Run-Test/Idle state. The

nINIT_CONF

pin is then released and nCONFIG is pulled high by the

resistor after the JTAG state machine goes out of Run-Test/Idle state.

The FPGA configuration starts after the nCONFIG pin goes high. As a

result, the FPGA is configured with the new configuration data stored

in the configuration device. You can add this function to your

programming file (.pof, .jam, .jbc) in the Quartus II software by

enabling the Initiate configuration after programming option in the

Programmer options window (Options menu). This instruction is

also used by the MAX+PLUS II software, .jam files, and .jbc files.

ISP Instructions

—

These instructions are used when programming an EPC2 device

using JTAG ports with a USB-Blaster, MasterBlaster, ByteBlaster II,

EthernetBlaster, or ByteBlasterMV download cable, or using a .jam,

.jbc, or .svf file using an embedded processor.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNY267GN-TL | IC OFFLINE SWIT OTP OCP HV 8SMD |

| GRM1885C2A361JA01D | CAP CER 360PF 100V 5% NP0 0603 |

| XC17S30AVO8C | IC PROM SER 300K 8-SOIC |

| FMM18DSEH | CONN EDGECARD 36POS .156 EYELET |

| EPC2TI32 | IC CONFIG DEVICE 1.6MBIT 32-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPC3.3SC36-A | 功能描述:DC/DC轉(zhuǎn)換器 50 Watts 3.3 Volts RoHS:否 制造商:Murata 產(chǎn)品: 輸出功率: 輸入電壓范圍:3.6 V to 5.5 V 輸入電壓(標稱): 輸出端數(shù)量:1 輸出電壓(通道 1):3.3 V 輸出電流(通道 1):600 mA 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風格:SMD/SMT 封裝 / 箱體尺寸: |

| EPC30 | 制造商:TDK 制造商全稱:TDK Electronics 功能描述:Ferrite Cores For Power Supply and Signal Transformer EPC Cores |

| EPC300 | 制造商:EPC 制造商全稱:EPC 功能描述:High sensitive photodiodes |

| EPC3001 | 制造商:PCA 制造商全稱:PCA ELECTRONICS INC. 功能描述:Flyback Transformer |

| EPC3005 | 制造商:PCA 制造商全稱:PCA ELECTRONICS INC. 功能描述:Flyback Transformer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。