- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19910 > EPC2TI32N (Altera)IC CONFIG DEVICE 1.6MBIT 32-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | EPC2TI32N |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 9/26頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC CONFIG DEVICE 1.6MBIT 32-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 250 |

| 系列: | EPC |

| 可編程類(lèi)型: | 系統(tǒng)內(nèi)可編程 |

| 存儲(chǔ)容量: | 1.6Mb |

| 電源電壓: | 3 V ~ 3.6 V,4.5 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 32-TQFP |

| 供應(yīng)商設(shè)備封裝: | 32-TQFP(7x7) |

| 包裝: | 托盤(pán) |

| 產(chǎn)品目錄頁(yè)面: | 604 (CN2011-ZH PDF) |

| 其它名稱(chēng): | 544-1648 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

Timing Information

Page 17

Configuration Devices for SRAM-Based LUT Devices

January 2012

Altera Corporation

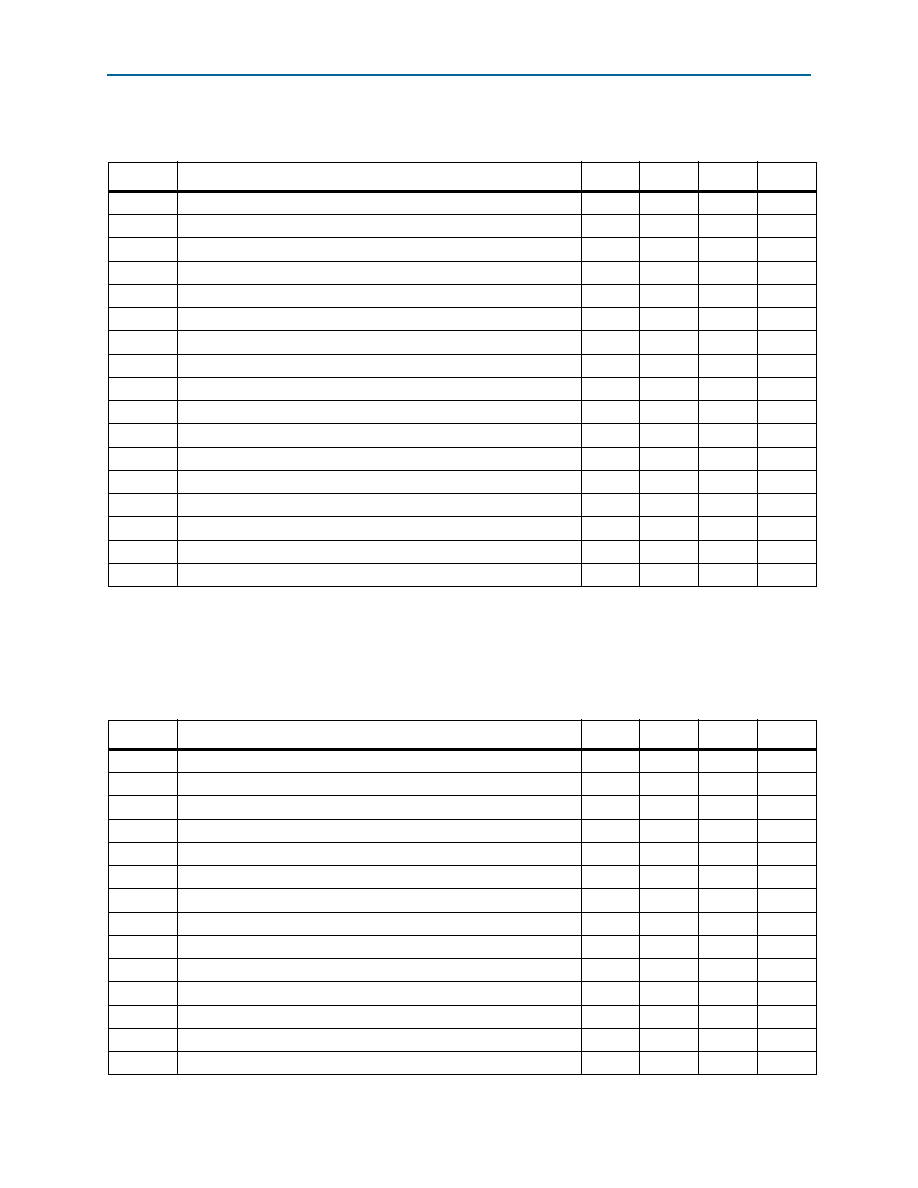

Table 9 lists the timing parameters when using EPC1 and EPC1441 devices at 3.3 V.

Table 10 lists the timing parameters when using EPC1, EPC2, and EPC1441 devices at

5.0 V.

Table 9. Timing Parameters when Using EPC1 and EPC1441 Devices at 3.3 V

Symbol

Parameter

Min

Typ

Max

Units

tPOR

POR delay (1)

——

200

ms

tOEZX

OE

high to DATA output enabled

—

80

ns

tCE

OE

high to first rising edge on DCLK

——

300

ns

tDSU

Data

setup time before rising edge on DCLK

30

—

ns

tDH

Data

hold time after rising edge on DCLK

0—

—

ns

tCO

DCLK

to DATA out

—

30

ns

tCDOE

DCLK

to DATA enable/disable

—

30

ns

fCLK

DCLK

frequency

2

4

10

MHz

tMCH

DCLK

high time for the first device in the configuration chain

50

125

250

ns

tMCL

DCLK

low time for the first device in the configuration chain

50

125

250

ns

tSCH

DCLK

high time for subsequent devices

50

—

ns

tSCL

DCLK

low time for subsequent devices

50

—

ns

tCASC

DCLK

rising edge to nCASC

—

25

ns

tCCA

nCS

to nCASC cascade delay

—

15

ns

tOEW

OE

low pulse width (reset) to guarantee counter reset

100

—

ns

tOEC

OE

low (reset) to DCLK disable delay

—

30

ns

tNRCAS

OE

low (reset) to nCASC delay

—

30

ns

Note to Table 9:

(1) During initial power-up, a POR delay occurs to permit voltage levels to stabilize. Subsequent reconfigurations do not incur this delay.

Table 10. Timing Parameters when Using EPC1, EPC2, and EPC1441 Devices at 5.0 V (Part 1 of 2)

Symbol

Parameter

Min

Typ

Max

Units

tPOR

POR delay (1)

——

200

ms

tOEZX

OE

high to DATA output enabled

—

50

ns

tCE

OE

high to first rising edge on DCLK

——

200

ns

tDSU

Data

setup time before rising edge on DCLK

30

—

ns

tDH

Data

hold time after rising edge on DCLK

0—

—

ns

tCO

DCLK

to DATA out

—

20

ns

tCDOE

DCLK

to DATA enable/disable

—

20

ns

fCLK

DCLK

frequency

6.7

10

16.7

MHz

tMCH

DCLK

high time for the first device in the configuration chain

30

50

75

ns

tMCL

DCLK

low time for the first device in the configuration chain

30

50

75

ns

tSCH

DCLK

high time for subsequent devices

30

—

ns

tSCL

DCLK

low time for subsequent devices

30

—

ns

tCASC

DCLK

rising edge to nCASC

—

20

ns

tCCA

nCS

to nCASC cascade delay

—

10

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNY267GN-TL | IC OFFLINE SWIT OTP OCP HV 8SMD |

| GRM1885C2A361JA01D | CAP CER 360PF 100V 5% NP0 0603 |

| XC17S30AVO8C | IC PROM SER 300K 8-SOIC |

| FMM18DSEH | CONN EDGECARD 36POS .156 EYELET |

| EPC2TI32 | IC CONFIG DEVICE 1.6MBIT 32-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPC3.3SC36-A | 功能描述:DC/DC轉(zhuǎn)換器 50 Watts 3.3 Volts RoHS:否 制造商:Murata 產(chǎn)品: 輸出功率: 輸入電壓范圍:3.6 V to 5.5 V 輸入電壓(標(biāo)稱(chēng)): 輸出端數(shù)量:1 輸出電壓(通道 1):3.3 V 輸出電流(通道 1):600 mA 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風(fēng)格:SMD/SMT 封裝 / 箱體尺寸: |

| EPC30 | 制造商:TDK 制造商全稱(chēng):TDK Electronics 功能描述:Ferrite Cores For Power Supply and Signal Transformer EPC Cores |

| EPC300 | 制造商:EPC 制造商全稱(chēng):EPC 功能描述:High sensitive photodiodes |

| EPC3001 | 制造商:PCA 制造商全稱(chēng):PCA ELECTRONICS INC. 功能描述:Flyback Transformer |

| EPC3005 | 制造商:PCA 制造商全稱(chēng):PCA ELECTRONICS INC. 功能描述:Flyback Transformer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。